## Testing specification for the wafer screening Project Name: ABCD3T ASIC Version: V1.3, 1 December, 2000

| 1.          | SCOPE                    |                                                                                 |                             |  |  |

|-------------|--------------------------|---------------------------------------------------------------------------------|-----------------------------|--|--|

| 2.          | RE                       | FERENCE DOCUMENTS                                                               | 4                           |  |  |

| 3.          | WA                       | AFER SCREENING SYSTEM                                                           | 5                           |  |  |

| 3           | .1.                      | Reliability issues                                                              | 5                           |  |  |

| 3           | .2.                      | Quality of the analogue measurements                                            | 6                           |  |  |

| 4.          | FL                       | OW OF TESTS                                                                     | 7                           |  |  |

| 5.          | РО                       | WER CONSUMPTION MEASUREMENT                                                     | 9                           |  |  |

| 6.          | DE                       | SCRIPTION OF THE ANALOGUE TESTS                                                 | 10                          |  |  |

| 6           | .1.                      | Gain, offset and noise characterization                                         | 10                          |  |  |

| 6           | .2.                      | Characterization of the TRIM DAC's                                              | 10                          |  |  |

| 6           | .3.                      | Characterization of the TRIM DAC range                                          | 11                          |  |  |

| 7.<br>CO    |                          | EASUREMENT OF THE CHARACTERISTICS OF THE DIGITAL-TO-ANALOGUI                    |                             |  |  |

| 8.          | DE                       | SCRIPTION OF THE BLOCK OF DIGITAL TESTS (DRAFT/SEQSI SETUP)                     | 13                          |  |  |

| 8           | .1.                      | TEST #1, configuration register input/output test                               | 13                          |  |  |

| 8           | .2.                      | TEST #2, addressing test                                                        | 14                          |  |  |

| 8           | .3.                      | TEST #3, input register test                                                    | 14                          |  |  |

| 8           | .4.                      | TEST #4, input lines test                                                       | 15                          |  |  |

| 8           | .5.                      | TEST #5, Fake Slave Test                                                        | 15                          |  |  |

| 8           | .6.                      | TEST #6, slave test                                                             | 16                          |  |  |

| 9.          | DI                       |                                                                                 |                             |  |  |

| 4.0         | DI                       | GITAL TESTS AT IMS TESTER                                                       | 16                          |  |  |

| 10.         |                          | GITAL TESTS AT IMS TESTER                                                       |                             |  |  |

|             |                          |                                                                                 | 16                          |  |  |

| 1           | Ι                        | FLOW OF DATA                                                                    | <b>16</b>                   |  |  |

| 1           | <b>I</b><br>0.1.         | FLOW OF DATA                                                                    | <b>16</b><br>16<br>17       |  |  |

| 1<br>1<br>1 | <b>I</b><br>0.1.<br>0.2. | FLOW OF DATA<br>Format of the ROOT file<br>Definition of BIN and yield analysis | <b>16</b><br>16<br>17<br>20 |  |  |

#### 1. Scope

This document describes the environment and requirements for testing of the ABCD3T chip for readout of silicon strip detectors for ATLAS SCT. It is meant to provide pass/fall criteria for each chip based on analysis of data taken during the wafer screening of the ABCD3T chips.

The wafer testing system should complete two tasks:

- Qualification of good chips to be delivered for the SCT detector (Database filled with all electrical parameters and coordinates of the chip on the wafer to check that chips are delivered according to the specification).

- Yield analysis, which is a part of the design validation and control of the process stability during the production (generation of bin files, which are used as inputs for the bin analysis performed in the foundry (TEMIC)).

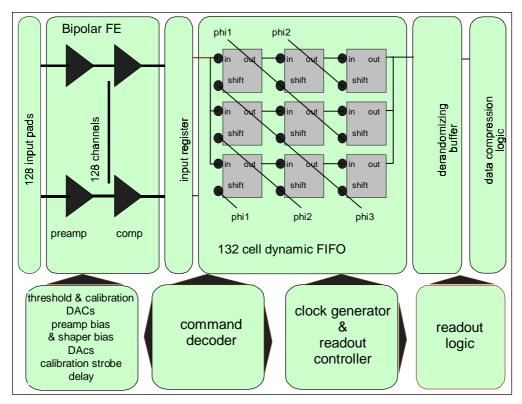

The architecture of the ABCD3T chip and full specification is described in the "ABCD3T Chip, Project specification, Version V1.1" document [1]. The simplified block diagram of the ABCD3T chip is shown in figure 1.

Figure 1: Block diagram of the ABCD3T chip.

Functionally the ABCD3T chip can be split in to two main blocks:

- Analogue front-end containing 128 channels of fast transimpedance amplifiers and comparators, digital-toanalogue converters and calibration circuit (about 30000 BiCMOS devices placed on 5mm<sup>2</sup>)

- Digital part containing the input register, pipeline, derandomizing buffer, command decoder, readout logic, and threshold & calibration control (about 200000 CMOS devices laid out on 46mm<sup>2</sup> silicon area).

The functionality of the analogue part of the chip is tested using internal calibration circuitry. Each channel has an internal calibration capacitor connected to its input for purposes of simulating a "hit" strip. The calibration capacitors are charged by an internal chopper circuit, which is triggered by a command. Every fourth channel can be tested simultaneously with group selection determined by two binary coded calibration address inputs (CALD0, CALD1). The strobe and the address signals are delivered from the control block. The voltage applied to the calibration capacitors by the chopper is determined by an internal DAC. A tuneable delay of the calibration strobe with respect to the clock phase covering at least two clock periods is provided.

The whole digital part of the chip is tested separately using test vectors inserted into the input register, which is the parallel I/O interface between analogue and digital parts of the chip.

Internal testability features implemented in the design allow testing of the analogue performance via digital control signals adhering to the LVDS standards. This solution offers the possibility of precise measurement of analogue parameters during the wafer screening.

The calibration signals processed in the amplifier and comparator can be read-out only through the digital part of the chip. A consequence of this is that an estimation of the yield of the analogue part can only be performed for that subset of chips which pass the digital tests.

## 2. Reference documents

- 1. ABCD3T Chip, Project Specification, Version V1.1

- 2. Description of the wafer Screening Data Analysis Software: http://ific.uv.es/~lacasta/WaferScreening/

- 3. W. Dabrowski, et al., "Fast Bipolar Front-end for Binary Readout of Silicon Strip Detectors", Nuclear Instruments and Methods A 350 (1994), 548.

- 4. Description of the ROOT package: <u>http://root.cern.ch</u>

- 5. W. Dabrowski, J. Kaplon, R. Szczygiel "SCT128B a prototype chip for binary readout of silicon strip detectors", Nuclear Instruments and Methods in Physics Research A 421 (1999) 303-315

- 6. W. Dabrowski, et al., "Performance of the Binary Readout of Silicon Strip Detectors Using the Radiation Hard SCT128B Chip", IEEE, Trans. Nucl. Sci. Vol. 45, No.3 (1998), 310.

- W. Dabrowski, et al., "The ABCD Binary Readout Chip for Silicon Strip Detectors in the Atlas Silicon Tracker", Proc. of the Fourth Workshop on Electronics for LHC Experiments, Rome, September 21-25, 1988, CERN/LHCC/98-36, p. 175.

- 8. W. Dabrowski, A proposal to implement individual threshold correction per channel in the ABCD chip.

- 9. ABCD2T/ABCD2NT ASIC, Project Specification V 2.1.

## 3. Wafer screening system

The test apparatus for wafer screening is based on a probe station with a fully motorised chuck stage whose movement is controlled through a GPIB interface. The chip control and data acquisition are based on user developed VME cards which provide the clock and control signals to the chip and decode the data from the tested device. An HP voltmeter with GPIB interface is used for testing the vacuum (which fixes the wafers to the chuck) during wafer probing. The whole system is controlled by a dedicated program written in C++ and running on a PC under Windows 95. The program controls the VME and the GPIB buses. It builds the commands to carry out the tests, reads out the VME modules, controls all the movements of the wafer prober, configures the power supplies, reads the power consumption and DC voltages from all test pads of the digital-to-analogue converters. Probe movements are carefully controlled and the entire system stops if any disagreement is found between the programmed and monitored coordinates or if the vacuum fails.

#### 3.1. Reliability issues

The high number of test vectors, long duration of the probing (1-4min) and complexity of the tests require a very reliable connection between the chip and the probe needles. Since we are using a custom design probe card with all digital signals buffered it is not possible to check the connections between the needles and the probed pads as in standard industrial probers by taking the DC characteristic of the protection devices before the execution of real tests. The biggest problem for the reliability of the connection is the oxidation and mechanical degradation of the needles during the probing. Depending on the material used for the needles (specification obtained from the probe card vendor) cleaning of the probe card needles is required every 30 (50) wafers. Since there is no way to check the quality of the connections between the chip and the probe card on-line it is necessary to check this during off-line data analysis. The proposed method is to look at the result of a scan of digital test block for different power supply voltages and frequencies. The specified scan is performed to extract the basic output parameters for digital tests:

- minimum Vdd at 40MHz BCO clock for 100% efficiency in the digital tests

- minimum Vdd at 50MHz BCO clock for 100% efficiency in the digital tests (or max. frequency at Vdd=4V).

These two parameters characterising the speed margin of the chips depend on two factors:

- actual parameters of the CMOS devices coming from the given run (slow, typical or fast corner of the process)

- quality of the connection between the needles and probe pads (higher resistance for the connection implies higher voltage drop on the power supply pads)

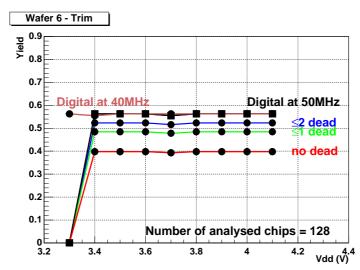

Analysing the number of chips passing the digital tests executed for different bias conditions (value of Vdd and BCO frequency) it is possible to plot the yield versus Vdd figure for a given wafer screened during one test run. An example of such a plot is shown in Figure 2. In the yield figure one can distinguish two regions:

- The flat part of the figure where the number of chips passed the tests is constant above some value of the Vdd. The fluctuations in this region indicate problems possibly due to unreliable chip contact.

- The transition region, where the number of chips passing the tests is changing. Widening of the transition region and moving it to the higher Vdd value indicates a problems with the probe contacts (assuming that wafers from the same run have the same speed performance).

Figure 2: Digital and analogue yield versus Vdd for 40 and 50MHz BCO clock.

#### 3.2. Quality of the analogue measurements

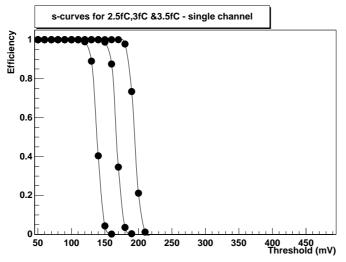

The measurement method to obtain the analogue parameters (gain, noise and offset) for the chip is fully described in reference [5]. The gain, offset and noise of the front-end can be evaluated by scanning the discriminator threshold for a given input charge applied from the internal calibration circuitry. For each threshold value a series of pulses is applied and the fraction of pulses which fire the comparator is measured. The threshold scan for a given input signal gives the so-called S-curve, i.e. counting rate as a fraction of triggers at the discriminator output as a function of the threshold. Provided the noise has a Gaussian amplitude distribution, the S-curve is described by the complementary error function. The 50% points of the S-curve correspond to a threshold equal to the signal amplitude while the width of the S-curve contains information about the r.m.s. value of noise. By performing these measurements for several values of the input charge one can extract the gain of all the circuitry preceding the discriminator and the discriminator input offset.

Figure 3: Example of the S-curves taken with 500 triggers (normalized to 1)

This measurement of the analogue performance requires the acquisition of clean S-curves (fitting well to the complementary error function) which means there should be a low level of excess noise and interference from the digital signals. Satisfying that requirement is essential to provide reliable fits during data analysis. Any crashing fit of a single S-curve to the complementary error function during offline data analysis will result in the generation of an artificial defect in the analogue part of the chip. For this reason, it is highly desirable to check the quality of fits in the case where chips show single defects in the analogue part only. Assuming a trigger rate in the range of 100-500 per scanned point it is necessary to keep the saturated noise occupancy (independent of the threshold) below  $10^{-3}$ . Example of S-curves for one of the channels of the tested chips is shown in Figure 3. The quality of data taken during wafer screening should provide a full characterization of the tested ABCD3T chips including also the noise measurement performed with some accuracy. The excess noise caused by the non-

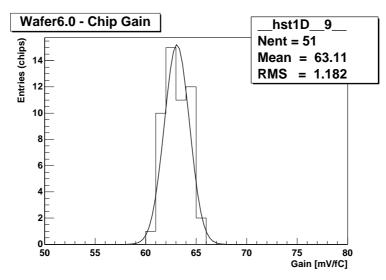

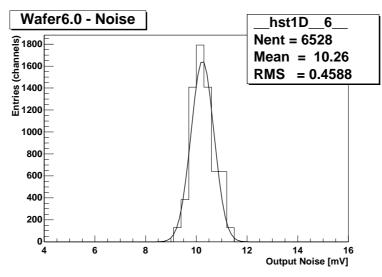

optimum assembling of the chip during probing should not be higher than the electronic noise coming from the input device (base current of the input transistor plus feedback resistor plus noise related to the parasitic input capacitance of the bonding pad). This gives a limit of about 1200e ENC of noise for a nominal bias current in the input BJT (220uA). The typical figure of gain and output noise obtained with an active probe card (CERN apparatus) is shown in figures 4 and 5 respectively. The calculated ENC is in the range of 1000e<sup>-</sup>, which has to be compared with 700e<sup>-</sup> noise obtained for the chip mounted on a hybrid and under the same bias conditions. The RMS spread of the noise between channels is only 50e<sup>-</sup>. This result allows us to make a reliable cut when looking for noisy channels in the analogue FE part (the value used for the cut is 2000e<sup>-</sup>).

Figure 4: Distribution of the mean values of the gain for one wafer from batch Z31122 (for the accepted chips)

Figure 5: Distribution of the output noise for one wafer from batch Z31122 (for the accepted chips)

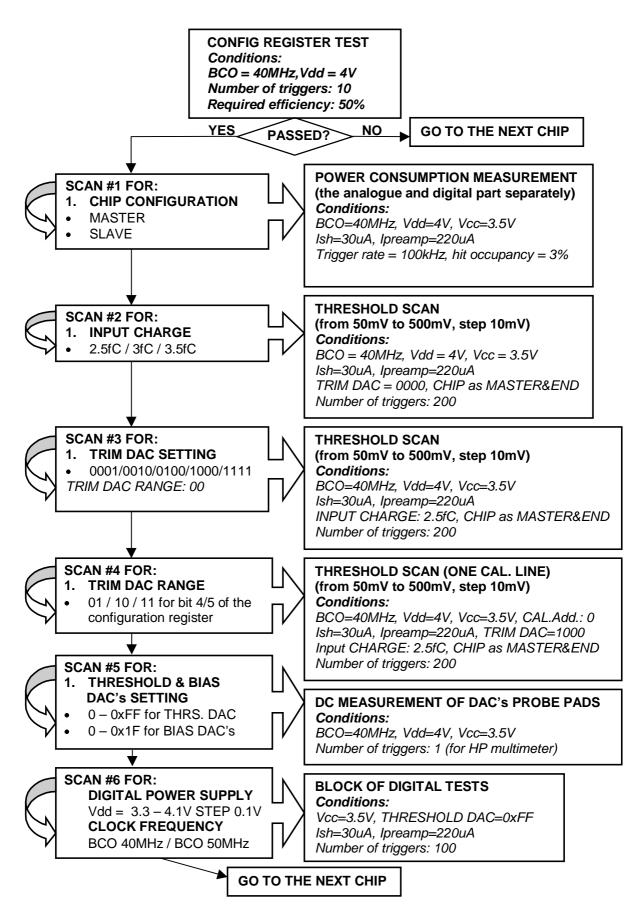

#### 4. Flow of tests

The wafer prober system provides a full parameterization of the ABCD3T chips. The test flow is shown in figure 6. The test starts with the configuration register test. All the chips passing this basic digital test for the nominal condition of power supply and speed are examined and the results are saved for off-line analysis and tagging. Skipping the chips failing the CONFIG REGISTER test accelerates the screening process. All remaining chips are tested without stopping due to the failure of any one test. This approach is driven by the necessity of having full information about the wafer in order to control the final yield and distribution of defects in various blocks of the chip.

Figure 6: Flow of tests executed during probing of a single ABCD3T chip.

The power consumption of the chip is measured separately in analogue and digital parts of the chip for nominal speed, bias, trigger rate and hit occupancy conditions, both in MASTER and SLAVE mode of operation. Analogue parameters (gain, noise, offset, and characteristic of TRIM DAC) are obtained by scanning the threshold for several levels of calibration signals. The characteristics of all digital-to-analogue converters are measured using the test probe pads. A number of tests are made to check all digital functionality. The full set of those tests is performed for different values of Vdd and frequency in order to extract the speed margins of the devices

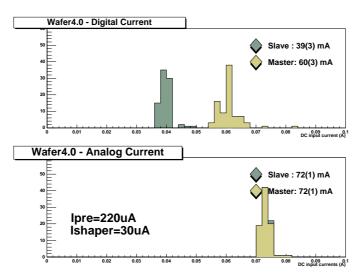

## 5. Power consumption measurement

The power consumption of both digital and analogue parts of the chip is measured. To simulate the nominal working conditions for the ATLAS SCT occupancy and L1 trigger rate, the measurement is done applying a 100kHz trigger with an occupancy of 3% (hits in 4 channels). ABCD3T chips with power consumption outside the standard distribution will be rejected due to possible weakness of some parts and potential limited reliability. The typical distribution of the power consumption of the ABCD chips working as slave or master for one wafer from batch Z31122 is shown in figure 7.

Figure 7: Distribution of the power consumption of the ABCD chips from batch Z31122.

|          | CHIP configuration |               |                                         | DATA_COMPRESSION_01X  <br>NG_MODE   SELECT_0 |  |

|----------|--------------------|---------------|-----------------------------------------|----------------------------------------------|--|

|          |                    | Ipreamp       |                                         | <b>220</b> μA                                |  |

|          |                    | Ishaper       |                                         | <b>30 μA</b>                                 |  |

| SETTINGS | CHIP bias          | Vcc           |                                         | 3.5 V                                        |  |

| Ž        |                    | Vdd           |                                         | 4 V                                          |  |

|          |                    | BCO           |                                         | 40 MHz                                       |  |

| SE       |                    | Threshold DAC |                                         | 0xFF                                         |  |

|          | TRIM DAC           | Value         |                                         | 0000                                         |  |

|          |                    | Range         |                                         | 00                                           |  |

|          | CHIP address       |               |                                         | Programmed = 1                               |  |

|          | COMMAND            | Issue C       | Calibrati                               | libration Pulse + 131 BCO delay + L1 trigger |  |

| SCANS    | LOOPS              |               | 1. Chip configuration = {MASTER, SLAVE} |                                              |  |

| sci      | Trigger rate       |               | 100 kH                                  | Z                                            |  |

Table 1: Power consumption measurement (SCAN #1, Figure 6).

## 6. Description of the analogue tests

During wafer screening all functions related to signal processing should be exercised and measured. The gain, offset and noise for each channel should be measured and stored in data file. During the wafer screening the measurement of the time walk is too time consuming. In order to capture those chips with a timing problem all threshold scans should be done with edge detection circuitry ON and data compression mode 01X. For each wafer the timing applied via calibration delay register should be verified. This can be accomplished by a threshold scan in EDGE mode and comparison of the offset extracted from response curves with the leading edge of the S-curves (for good timing these two values should be very close to each other).

#### 6.1. Gain, offset and noise characterization

The goal of the test is to determine the basic analogue parameters of the front-end: gain, noise and discriminator offset for each electronic channel. For this purpose threshold scans for three different input charges are done for each channel in the chip. The input transistor current and shaper current are set to nominal values and a 40MHz BCO clock drives the chip. Three S-curves per channel are fitted to a complementary error function. From the 50% points the gain curve is extracted and fitted to a straight line. The gain and the offset are taken as the slope and offset of the linear fit respectively. The electronic noise is obtained for each pulse from S-curve fit.

|          | CHIP configuration | MASTER  |                                                                                                                                               | ON   DATA_COMPRESSION_01X  <br>NG MODE   SELECT 0 |

|----------|--------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

|          |                    | Ipreamp |                                                                                                                                               |                                                   |

| S        |                    | Ishaper |                                                                                                                                               | 30 μΑ                                             |

| SETTINGS | CHIP bias          | Vcc     |                                                                                                                                               | 3.5 V                                             |

| Ē        |                    | Vdd     |                                                                                                                                               | 4 V                                               |

|          |                    | BCO     |                                                                                                                                               | 40 MHz                                            |

| S        | TRIM DAC           | Value   |                                                                                                                                               | 0000                                              |

|          |                    | Range   |                                                                                                                                               | 00                                                |

|          | CHIP address       |         |                                                                                                                                               | Programmed = 1                                    |

|          | COMMAND            |         | Issue Calibrati                                                                                                                               | on Pulse + 131 BCO delay + L1 trigger             |

| SCANS    | LOOPS              |         | <ol> <li>INPUT CHARGE = {2.5fC, 3fC, 3.5fC}</li> <li>CALIBRATION ADDRESS = {0,1,2,3}</li> <li>THRESHOLD = [50mV - 500mV] step 10mV</li> </ol> |                                                   |

| SC       | No. of triggers    |         | 200                                                                                                                                           |                                                   |

Table 2: Gain, noise and offset characterisation (SCAN #2, Figure 6).

#### 6.2. Characterization of the TRIM DAC's

In order to compensate channel-to-channel variation of the discriminator offset each channel is provided with a trim DAC of 4-bit resolution. Each channel can be addressed individually and the threshold correction can be applied channel by channel. The range of the trim DAC can be selected with two bits in the configuration register. For the TRIM DAC characterisation, a scan for a selected combination of settings is done for each electronic channel and for a fixed calibration pulse (2.5fC). Applying the same analysis described as for the gain and offset measurement, an overall characteristic of the TRIM DAC is obtained. The measurement is done for the basic range of the TRIM DAC (00). The measurement point for the TRIM DAC value = 0000 is taken from the previous measurement of the gain and offset (to limit the number of points in the scan).

|          | CHIP configuration | MAST    | MASTER   END   EDGE_ON   DATA_COMPRESSION_01X  <br>DATA_TAKING_MODE   SELECT_0                                                      |                |  |  |  |

|----------|--------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|--|

| S        |                    | Ipreamp |                                                                                                                                     | 220 μA         |  |  |  |

|          |                    | Ishaper |                                                                                                                                     | <b>30 μA</b>   |  |  |  |

| SETTINGS | CHIP bias          | Vcc     |                                                                                                                                     | 3.5 V          |  |  |  |

| Ē        |                    | Vdd     |                                                                                                                                     | 4 V            |  |  |  |

|          |                    | BCO     |                                                                                                                                     | 40 MHz         |  |  |  |

| S        | Input Charge       |         |                                                                                                                                     |                |  |  |  |

|          | TRIM DAC           | Range   |                                                                                                                                     | 00             |  |  |  |

|          | CHIP address       |         |                                                                                                                                     | Programmed = 1 |  |  |  |

|          | COMMAND            |         | Issue Calibration Pulse + 131 BCO delay + L1 trigger                                                                                |                |  |  |  |

| SCANS    | LOOPS              |         | 1. TRIM DAC VALUE = {0001, 0010, 0100, 1000, 1111}<br>2. CALIBRATION ADDRESS = {0,1,2,3}<br>3. THRESHOLD = [50mV - 500mV] step 10mV |                |  |  |  |

| SC       | No. of triggers    |         | 200                                                                                                                                 |                |  |  |  |

Table 3: Characterisation of the TRIM DAC's (SCAN #3, Figure 6).

#### 6.3. Characterization of the TRIM DAC range

The range of the trim DAC can be selected with two bits in the configuration register (see Table 3.10b in ref. [1]). This is to cover the offset spread, which is expected to increase after irradiation. There are four selectable ranges of the TRIM DAC.

| Trim DAC range<br>Bit 1 | Trim DAC range<br>Bit 0 | Trim DAC range | Trim DAC step |

|-------------------------|-------------------------|----------------|---------------|

| 0                       | 0                       | 0  mV - 60  mV | 4 mV          |

| 0                       | 1                       | 0mV -120 mV    | 8 mV          |

| 1                       | 0                       | 0mV -180 mV    | 12 mV         |

| 1                       | 1                       | 0mV -240 mV    | 16 mV         |

Table 4: Trim DAC range selection.

Since the goal of this measurement is to check the range of the TRIM DAC which is a common factor for all channels only one calibration line is used (calibration address 0). The scan for the TRIM DAC RANGE setting is performed for one TRIM DAC value (1000) and one calibration charge (2.5fC). The measurement point for TRIM DAC RANGE = 00 is taken from the previous scan. The TRIM DAC RANGE is calculated as an average of the values obtained from 32 scanned channels (calibration address 0).

|          | CHIP configuration  | MASTER   END   EDGE_ON   DATA_COMPRESSION_01X  <br>DATA_TAKING_MODE   SELECT_0 |                                                                             |                                         |  |

|----------|---------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------|--|

|          |                     | Ipreamp                                                                        |                                                                             | 220 μΑ                                  |  |

|          |                     | Ishaper                                                                        |                                                                             | 30 μA                                   |  |

| SETTINGS | CHIP bias           | Vcc                                                                            |                                                                             | 3.5 V                                   |  |

| Ž        |                     | Vdd                                                                            |                                                                             | 4 V                                     |  |

|          |                     | BCO                                                                            |                                                                             | 40 MHz                                  |  |

| Ш<br>Ш   | CALIBRATION address |                                                                                |                                                                             | 0                                       |  |

|          | Input Charge        |                                                                                |                                                                             | 2.5 fC                                  |  |

|          | TRIM DAC            | Value                                                                          |                                                                             | 1000                                    |  |

|          | CHIP address        |                                                                                |                                                                             | Programmed = 1                          |  |

|          | COMMAND             |                                                                                | Issue Calibrat                                                              | tion Pulse + 131 BCO delay + L1 trigger |  |

| SN       | LOOPS               |                                                                                | 1. TRIM DAC RANGE = {01, 10, 11}<br>2. THRESHOLD = [50mV - 500mV] step 10mV |                                         |  |

| SCANS    | No. of triggers     |                                                                                | 200                                                                         |                                         |  |

| Table 5: Characterisation | of TRIM DAC range | (SCAN #4, Figure 6). |

|---------------------------|-------------------|----------------------|

|---------------------------|-------------------|----------------------|

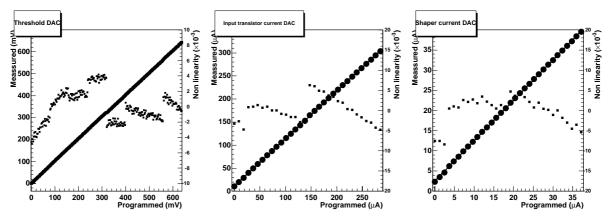

# 7. Measurement of the characteristics of the Digital-to-Analogue Converters

The ABCD3T chip has 3 main DACs, which must be tested:

- Threshold DAC (8 bits)

- Input transistor current DAC (Ipreamp 5 bit)

- Shaper current DAC (Ishaper 5 bit)

The chip incorporates one additional 8 bit DAC for the calibration pulse height, which is not directly tested and its failure will result in a deficient analogue performance. In order to check the characteristic of the DAC a full scan across the DAC settings is done and the DC levels provided by the chip at its test pads are readout. This allows a measurement of the linearity error, as shown in figure 8, where the relative deviation from linearity with respect to the DAC range is also depicted.

Figure 8: Linearity of the threshold and bias DACs. The round bullets show the DAC characteristic. The small square bullets show the deviation from linearity relative to the range of the DAC. Its scale is shown on the right axis.

The output of the threshold DAC is available directly at the pads VTHN and VTHP (Vthreshold = VTHP – VTHN). The outputs of the preamplifier and shaper bias DACs could be tested on the pads IP\_PROBE and

IS\_PROBE respectively. The conversion between value of the current at the DAC output and value of the voltage at the probe pad are described by following formulas:

$$V_{IP\_PROBE}[V] = I_{PREAMP}[A] \times 250 \times (R_{RLV\_NORM}/R_{RBXB\_NORM})$$

$$V_{IS\ PROBE}[V] = I_{SHAPER}[A] \times 1000 \times (R_{RLV\ NORM}/R_{RBXB\ NORM})$$

Where RRLV\_NORM and RRBXB\_NORM are normalised values for RLV and RBXB type resistors (actual value divided by the nominal value) and they may fluctuate from lot to lot due to the process variations. For nominal values of the parameters (resistors, Vbe and temperature) the range of the preamplifier bias DAC is about 300uA which corresponds to the 75mV signal at the IP\_PROBE pad. The range for the shaper bias DAC is about 38uA which is equivalent to 38mV signal at the IS\_PROBE pad.

## 8. Description of the block of digital tests (DRAFT/SEQSI setup)

A number of tests are applied to check all the digital functionality of the chip. The main characteristics to ascertain are related to chip control, inter-chip communication and data compression. All the tests make extensive use of two testing tools provided by the ABCD3T chip: pulsing the input register or generating output pattern through the mask register. To evaluate the performance of the chip in the different tests, four different patterns with a length of 128 bits are injected:

- a sequence of 128 ones (mask #1)

- a sequence of 010101...01 (mask #2)

- a sequence of 101010...10 (mask #3)

- mask #4 with a sequence simulating ones (hits) in channel: 1, 3, 5, 7, 9, 11, 13, 17, 18, 20, 22, 24, 26, 28, 30, 32, 34, 36, 38, 40, 42, 44, 46, 48, 50, 52, 54, 56, 58, 60, 62, 64, 66, 68, 100, 104, 108, 116, 124

In order to evaluate the performance of the chip in the MASTER&MIDDLE mode (Fake Slave Test), external data are generated in the sequencer to simulate appending data from the slave chip. The following channel pattern is used: 1, 2, 3, 4, 5, 10, 12, 14, 16, 18, 20, 22, 24, 26, 28, 30, 32, 34, 36, 38, 40, 42, 44, 46, 48, 50, 52, 54, 56, 58, 60, 62, 64, 66, 68, 100, 104, 108, 116, 124. To determine the speed margins of the device, the described block of digital tests is performed for different values of frequency and power supply (SCAN #6, Figure 6).

#### 8.1. TEST #1, configuration register input/output test

This is the most determinant test because it proves that the chip can be configured. The configuration register is written with random values, keeping the chip always as MASTER and END. The values are then compared with the data returned by the chip in the send identification mode. Since addressing is not meant to be tested here, the universal address is used.

|          | CHIP configuration | MASTER        | END   S                                                        | SEND_ID_MODE   SELECT_0 |

|----------|--------------------|---------------|----------------------------------------------------------------|-------------------------|

|          |                    | Ipreamp       |                                                                | <b>220</b> μA           |

| 50       | CHIP bias          | Ishaper       |                                                                | <b>30</b> μA            |

| SETTINGS |                    | Threshold DAC |                                                                | 0xFF                    |

| IE       | TRIM DAC           | Value         |                                                                | 0000                    |

| SE       |                    | Range         |                                                                | 00                      |

|          | CHIP address       |               | Universal address in command                                   |                         |

|          | COMMAND            |               |                                                                | L1 trigger              |

| SCANS    | LOOPS              |               | 1. Random setting of the remaining configuration register bits |                         |

| SC/      | No. of triggers    |               | 100                                                            |                         |

Table 6: Configuration register input/output test (digital TEST#1).

#### 8.2. TEST #2, addressing test

The chip is given a random address and is configured using that address. The value is compared with the one returned in the chip data. An extra test is done at this level: The L1 counter is followed and its value stored. It should start at 0 and increase in steps of 1.

|          | CHIP configuration |               |        | _ON   DATA_COMPRESSIO<br>D_MODE   SELECT_0 | N_01X         |

|----------|--------------------|---------------|--------|--------------------------------------------|---------------|

| s        |                    | Ipreamp       |        |                                            | <b>220</b> μA |

| SETTINGS | CHIP bias          | Ishaper       |        |                                            | 30 μA         |

|          |                    | Threshold DAC |        |                                            | 0xFF          |

|          | TRIM DAC           | Value         |        |                                            | 0000          |

| S        |                    | Range         |        |                                            | 00            |

|          | CHIP address       |               |        | Random                                     |               |

|          | COMMAND            |               |        |                                            | L1 trigger    |

| SCANS    | LOOPS              |               | 1. Ran | dom setting of address bits                |               |

| SC/      | No. of triggers    |               | 100    |                                            |               |

Table 7: Addressing test (digital TEST #2).

#### 8.3. TEST #3, input register test

To check the functionality of the mask register and data readout block (pipeline, readout buffer, data compression and LED output), the four (masks #1, #2, #3 and #4) patterns are loaded in the mask register and the input register is pulsed. Pulsing the input register issues one BCO clock pulse to the channels allowed by the mask register. The data patterns read out from the chip are compared with the ones which are expected.

|          | CHIP configuration |               | MASTER   END   EDGE_ON   DATA_COMPRESSION_01X  <br>DATA_TAKING_MODE   SELECT_0 |                                           |  |  |  |

|----------|--------------------|---------------|--------------------------------------------------------------------------------|-------------------------------------------|--|--|--|

| S        |                    | Ipreamp       |                                                                                | 220µA                                     |  |  |  |

| 9        | CHIP bias          | Ishaper       |                                                                                | 30μΑ                                      |  |  |  |

| SETTINGS |                    | Threshold DAC |                                                                                | 0xFF                                      |  |  |  |

|          | TRIM DAC           | Value         |                                                                                | 0000                                      |  |  |  |

| S        |                    | Range         |                                                                                | 00                                        |  |  |  |

|          | CHIP address       |               |                                                                                | Programmed = 1                            |  |  |  |

|          | COMMAND            | Pulse Inp     |                                                                                | out Register + 129 BCO delay + L1 trigger |  |  |  |

| SCANS    | LOOPS              |               | 1. MASK = {mask#1, mask#2,mask#3,mask#4}                                       |                                           |  |  |  |

| SCI      | No. of triggers    |               | 100                                                                            |                                           |  |  |  |

Table 8: Input register test (digital TEST #3).

#### 8.4. TEST #4, input lines test

The functionality of both input lines for the chip (basic 0 and redundant 1) is tested by injecting the four patterns (masks #1, #2, #3 and #4) through the mask register and sending the clocks and commands through both lines. The delay between SoftReset and L1 trigger is scanned in order to examine each row of the pipeline (pipeline is a structure of 12 multiplexed rows). The data output is contrasted with the patterns. A token output is stored and checked.

|          | CHIP configuration | MAST     | MASTER   END   EDGE_OFF   DATA_COMPRESSION_X1X  <br>MASK   DATA_TAKING_MODE   SELECT_0                                              |                                |  |  |  |

|----------|--------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|--|--|

| S        |                    | Ipreamp  |                                                                                                                                     | 220µA                          |  |  |  |

| SETTINGS | CHIP bias          | Ishaper  |                                                                                                                                     | 30µA                           |  |  |  |

|          |                    | Threshol | d DAC                                                                                                                               | 0xFF                           |  |  |  |

|          | TRIM DAC           | Value    |                                                                                                                                     | 0000                           |  |  |  |

| S        |                    | Range    |                                                                                                                                     | 00                             |  |  |  |

|          | CHIP address       |          |                                                                                                                                     | Programmed = 1                 |  |  |  |

|          | COMMAND            |          |                                                                                                                                     | SoftReset + Delay + L1 trigger |  |  |  |

| SCANS    | LOOPS              |          | <ol> <li>SELECT LINE = {0,1}</li> <li>MASK = {mask#1, mask#2,mask#3,mask#4}</li> <li>Delay = [150BCO - 161BCO] step 1BCO</li> </ol> |                                |  |  |  |

| SC       | No. of triggers    |          | 10                                                                                                                                  |                                |  |  |  |

Table 9: Input lines test (digital TEST #4).

#### 8.5. TEST #5, Fake Slave Test

The chip is set as a master and middle chip. In the first part of the test the token transmission through both lines (0 and 1) is checked. In a second stage, a sequence simulating the data of a slave chip is injected through both input lines of the chip and contrasted with its output. The chip is also provided with a pattern programmed in the mask register in order to check that it merges its data properly with that of the slave.

|          | CHIP configuration |                                                                                        | E_ON   DATA_COMPRESSION_01X  <br>NG_MODE   SELECT_0 |  |

|----------|--------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------|--|

|          |                    | Ipreamp                                                                                | 220μΑ                                               |  |

| SETTINGS | CHIP bias          | Ishaper                                                                                | 30μΑ                                                |  |

| Ž        |                    | Threshold DAC                                                                          | 0xFF                                                |  |

|          | TRIM DAC           | Value                                                                                  | 0000                                                |  |

| SE       |                    | Range                                                                                  | 00                                                  |  |

|          | CHIP address       | Programmed                                                                             |                                                     |  |

|          | COMMAND            | Pulse Input Register + 129 BCO delay + L1 trigger + 5BCO delay + appended data pattern |                                                     |  |

| SNA      | LOOPS              | 1. {DATA_IN_0 & TOKEN_OUT_0, DATA_IN_1 & TOKEN_OUT_1<br>100                            |                                                     |  |

| SCANS    | No. of triggers    |                                                                                        |                                                     |  |

Table 10: Fake slave test (digital TEST #5).

#### 8.6. TEST #6, slave test

The chip is set as slave and end chip. The four patterns are injected through the mask register (mask#1, #2, #3 and #4) and the 8 tokens sent after each 8 triggers (to scan the derandomiser), through both input lines. The chip output is also searched on those lines.

|          | CHIP configuration | SLAVE   END   EDGE_OFF   DATA_COMPRESSION_X1X  <br>MASK   DATA_TAKING_MODE   SELECT_0 |       |  |

|----------|--------------------|---------------------------------------------------------------------------------------|-------|--|

| S        |                    | Ipreamp                                                                               | 220μΑ |  |

| SETTINGS | CHIP bias          | Ishaper                                                                               | 30μΑ  |  |

|          |                    | Threshold DAC                                                                         | 0xFF  |  |

|          | TRIM DAC           | Value                                                                                 | 0000  |  |

| S        |                    | Range                                                                                 | 00    |  |

|          | CHIP address       | Programmed = 1                                                                        |       |  |

|          | COMMAND            | 8xL1 trigger + 8xTOKEN                                                                |       |  |

| S        | LOOPS              | 1. {TOKEN_IN_0 & DATA_OUT_0, TOKEN_IN_1 & DATA_OUT_1}                                 |       |  |

| SCANS    |                    | <pre>2. MASK = {mask#1, mask#2,mask#3,mask#4}</pre>                                   |       |  |

| sc       | No. of triggers    | 10                                                                                    |       |  |

Table 11: Slave test (digital TEST #6).

## 9. Digital tests at IMS tester

In order to match the results obtained with two different hardware apparatus used for testing of the ABCD3T chips (DRAFT/SEQSI setup and IMS tester) a full compatibility between digital tests is provided. The stimulus vectors generated in Verilog covers the same digital tests (TEST#1 – TEST#6), giving the same types of results.

## 10. Flow of data

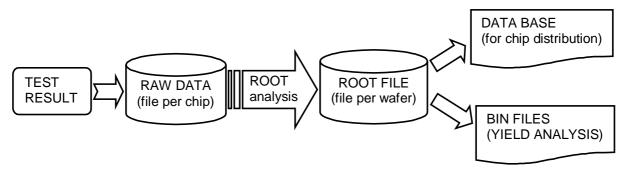

Results of all tests together with the chip coordinates on the wafer are saved on HD. One file per chip is created during the screening. Raw data from the whole wafer is analyzed using the ROOT package. One root file is created for the whole wafer. It contains many predefined histograms with the parameters extracted from the scans. Information about the position on the wafer, chip performance, wafer and batch reference is stored in this file. The root files are used to extract the information for user database and to produce the bin files used in yield analysis. The flow of data is shown in figure 9.

Figure 9: Flow of data extracted from the screened wafers with the ABCD3T chips.

#### 10.1. Format of the ROOT file

As mentioned above the raw data is processed and the information compiled using the ROOT packages into socalled *root files*. ROOT is a general purpose C++ package for data manipulation [4]. The environment created with ROOT for the wafer screening setup follows a hierarchical architecture, as data does. Four classes are defined: Wafer, Chip, Channel and ScanPoint. They reflect how the data are organised: A wafer has chips with a number of channels on which we perform a number of tests: the points in a scan of some of their parameters. In the root file, every class is stored in a sort of list, a Ttree in the ROOT jargon. The Wafer tree contains the Wafer class, which knows about the number of chips it contains and where they are located in the Chip Ttree. The same occurs with the Channel Ttree w.r.t the Chip Ttree and the ScanPoint Ttree w.r.t the Channel Ttree. On top of that, every class contains all the information of the screening configuration. The Chip class will contain information about the bias, digital test performed on it, etc, while a channel will contain information about which parameters have been scanned and over which range. A ScanPoint class will contain the information of the actual values of the scan point for a channel. Also every class is able to produce summaries about any parameter of the classes below it in the hierarchical tree. For instance the Chip class will be able to survey the noise of the channels for any of the scan points, that is, for any input calibration pulse. More detailed information about these files can be found in the description of the software [2].

This structure of the data eases the analysis and reduction of the information. It helps in preparing the data in all the formats needed in further steps of the testing process like building the database for chip distribution or the data files needed by the vendor for the yield analysis.

#### 10.2. Definition of BIN and yield analysis

As was mentioned at the beginning of this document, the described system for wafer screening should provide input for the yield analysis of the ABCD3T chips. The basis for the yield analysis is the bin file. The format of the bin file is accepted by the TEMIC foundry and it allows bin analysis to control and possibly improve the yield during the production of the ABCD3T chips. A chip can obtain only one bin number, which is the result of all tests performed on this die (to be compatible with the software used in TEMIC allowing for yield analysis). The definitions of the bins include all pass/fail criteria for the ABCD3T chips (bin 0 - chip accepted etc.). The result of the digital test is taken for a given value of power supply and frequency. This value is set in the flat region of the yield versus Vdd figure (see figure 3). For batches Z29476, Z30423 and Z31122, Vdd = 3.8V and a frequency of 50MHz were used as threshold parameters for the digital tests. Definition of the bins is shown in table 12. The ROOT macro used for the production of the bin files is described in the document [2].

| BIN | DEFINITION                                                                          |

|-----|-------------------------------------------------------------------------------------|

| 0   | Good chip (after all tests)                                                         |

| 2   | failed DIGITAL TEST#1 @ 3.8V & 50MHz                                                |

| 3   | failed DIGITAL TEST#2 (ADDRESSING) @ 3.8V & 50MHz                                   |

| 4   | failed DIGITAL TEST#2 (L1 counter) @ 3.8V & 50MHz                                   |

| 5   | failed DIGITAL TEST#4 (reading the mask) @ 3.8V & 50MHz                             |

| 6   | failed DIGITAL TEST#5 @ 3.8V & 50MHz                                                |

| 7   | failed DIGITAL TEST#6 @ 3.8V & 50MHz                                                |

| 8   | failed DIGITAL TEST#4 (reading the token) @ 3.8V & 50MHz                            |

| 9   | defect(s) in analog part #2 (channel offset out of the Trim DAC range 1 or          |

|     | discrepancy between gain and average gain higher than 25% or channel noise is       |

|     | 3 times higher than average noise of the chip <b>or</b> discrepancy between average |

|     | gain of the chip and average gain from the wafer is higher than 30%)                |

| 10  | defect(s) in analog part #1 (no response to the calibration pulses )                |

| 11  | between 1 to 10 defects in the pipeline (low analog efficiency)                     |

| 12  | ]10-100] defects in the pipeline (low analog efficiency)                            |

| 13  | > 100 defects in the pipeline (low analog efficiency)                               |

| 14  | high power consumption in digital part (Slave mode) (> 30% average <sup>1</sup> )   |

| 15  | high power consumption in analog part (Slave mode) (> 30% average)                  |

| 16  | low power consumption in digital part (Slave mode) (<30% average)                   |

| 17  | low power consumption in analog part (Slave mode) (<30% average)                    |

| 18  | Non-linear Threshold DAC (MAX ERR>10%)                                              |

| 19  | Non-linear Bias1 (Preamp) DAC (MAX ERR>25%)                                         |

| 20  | Non-linear Bias2 (Shaper) DAC (MAX ERR>25%)                                         |

| 21  | Defect in the TRIM DAC (MAX ERR>25% or discrepancy between Trim DAC                 |

|     | range 0 for a given channel and <b>TrDACRange0</b> is higher than 40%)              |

| 22  | Defect in Trim DAC ranges (discrepancies between <b>TrDACRange0</b> ÷               |

|     | <b>TrDACRange3</b> and averages from the wafer are higher than 40%)                 |

Table 12: Definition of the bins

<sup>&</sup>lt;sup>1</sup> Average of power consumption is calculated from the ABCD chips passing the digital tests (bins  $2 \div 8$ ).

Assignment of only a single bin to each chip compresses the information available from the root file. It allows for a simple correlation analysis to be performed between the bin files and the results of the process control monitoring test structures and map of defects performed at TEMIC. The sequence in which we define the bin for a given chip is important and may influence the eventual location of the defects on the chip. The algorithm for assigning bins to chips is shown in figure 10. Two types of the bin files are produced during the test analysis. Type "1" bin file comprising the list of the chips and their coordinates on the wafer and the bin result (one bin file per wafer). Type "2" bin file contains the list of the wafers for a given batch with the summary of bins for each wafer (one bin file per batch).

|               | 1. Digital power consumption 30% higher    | ? (YES) $\rightarrow$ bin = 14 $\rightarrow$ STOP)  |

|---------------|--------------------------------------------|-----------------------------------------------------|

|               | 2. Digital power consumption 30% lower ?   | $P (YES) \rightarrow bin = 16 \rightarrow STOP$     |

|               | 3. Failed DIGITAL TEST#1 ?                 | $(YES) \rightarrow bin = 2 \rightarrow STOP$        |

|               | 4. Failed DIGITAL TEST#2 (ADDRESSIN        | G)?(YES) $\rightarrow$ bin = 3 $\rightarrow$ STOP   |

| $\rightarrow$ | 5. Failed DIGITAL TEST#2 (L1 counter) ?    | $(YES) \rightarrow bin = 4 \rightarrow STOP$        |

|               | 6. Failed DIGITAL TEST#4 (MASK) ?          | $(YES) \rightarrow bin = 5 \rightarrow STOP$        |

|               | 7. Failed DIGITAL TEST#5 ?                 | $(YES) \rightarrow bin = 6 \rightarrow STOP$        |

|               | 8. Failed DIGITAL TEST#6 ?                 | $(YES) \rightarrow bin = 7 \rightarrow STOP$        |

|               | 9. Failed DIGITAL TEST#4 (TOKEN) ?         | $(YES) \rightarrow bin = 8 \rightarrow STOP$        |

|               | 10. More than 100 defects in pipeline ?    | $(YES) \rightarrow bin = 13 \rightarrow STOP$       |

|               | 11. Between ]10-100] defects in pipeline ? | P (YES) $\rightarrow$ bin = 12 $\rightarrow$ STOP   |

|               | 12. Between [1-10] defects in pipeline ?   | $(YES) \rightarrow bin = 11 \rightarrow STOP$       |

|               | 13. Analog power consumption 30% highe     | er? (YES) $\rightarrow$ bin = 15 $\rightarrow$ STOP |

|               | 14. Analog power consumption 30% lower     | r? (YES) $\rightarrow$ bin = 17 $\rightarrow$ STOP  |

| $\sim$ NO     | 15. Non-linear bias DAC #2 ?               | $(YES) \rightarrow bin = 20 \rightarrow STOP$       |

|               | 16. Non-linear bias DAC #1 ?               | $(YES) \rightarrow bin = 19 \rightarrow STOP$       |

| $\sim$ NO     | 17. Defect(s) in Trim DAC range?           | $(YES) \rightarrow bin = 22 \rightarrow STOP$       |

|               | 18. Defect(s) in analog (no response) ?    | $(YES) \rightarrow bin = 10 \rightarrow STOP$       |

|               | 19. Defect(s) in analog (high offset) ?    | $(YES) \rightarrow bin = 9 \rightarrow STOP$        |

|               | 20. Defect(s) in Trim DAC?                 | $(YES) \rightarrow bin = 21 \rightarrow STOP$       |

|               | 21. Non-linear threshold DAC ?             | $(YES) \rightarrow bin = 18 \rightarrow STOP$       |

|               |                                            |                                                     |

| ι             | 22. Accepted chips                         | $GOOD) \rightarrow bin = 0 \rightarrow STOP$        |

#### Figure10: Algorithm for binning the test results.

One can see that in the bin analysis the result of the digital TEST#3 (input register test) is not used. Since during this test the input register feeding the pipeline with the test pulse is still connected to the front-end amplifier/comparator, channels with very low offset (defect in analogue part) may affect the result of this test. This effect may influence mapping of the defects (defects in the analogue part may be localised in the pipeline). An extra cross check is used when we look for the defects in the pipeline not detected by the digital TEST#4 (input lines test). Because of the multiplexed structure, defects in the pipeline affect the efficiency of the analogue scans. Looking at the efficiency of the S-curves obtained during the threshold scans, one can find defects in the pipeline. In this way a bins with number 10, 11 and 12 are obtained. Nevertheless the result of the digital TEST#3 is used during the selection of the good chips with no defects.

The examples of the bin files are shown in figure 11a and 11b.

| [BEGIN OF FILE]<br>Z31122,990T,06,6,20,14<br>Z31122,990T,06,5,20,10 |

|---------------------------------------------------------------------|

|                                                                     |

|                                                                     |

| Z31122,990T,06,4,19,0                                               |

| Z31122,990T,06,3,19,6                                               |

| Z31122,990T,06,7,18,14                                              |

| Z31122,990T,06,6,18,5                                               |

| [END OF FILE                                                        |

Figure 11a: Example of bin file type 1 for wafer 6, batch31122

Figure 11b: Example of summary bin file for batch Z31122 (type 2)

The different parameters in the first line of figure 11a mean:

- Z31122 : Lot number

- 990T : TEMIC reference probe step

- 06, : Wafer number

- 6,20 : Chip X,Y position

- 14 : Bin Results

The different parameters in the first line of figure 11b mean:

| Z31122 | : | Lot | number |  |

|--------|---|-----|--------|--|

|--------|---|-----|--------|--|

- 990T : TEMIC reference probe step

- 2 : Wafer number

- 35 : sum of die with the bin number 0 (ie; the sum of good die)

- 0 : sum of die with the bin number 1

- 3 : sum of die with the bin number 2

- .

In this file a comma is placed at the end of each line. The last line of this file contains the following information:

| $L_{J1122}$ . Lot numbe | Z31122 | : | Lot | numbe |

|-------------------------|--------|---|-----|-------|

|-------------------------|--------|---|-----|-------|

- 990T : Our reference probe step

- : no reference wafer number: comma is placeholder

- 48 : average of the first bin of the lot (bin number 0)

- 0 : average of the second bin of the lot (bin number 1)

- 0 : average of the third bin of the lot (bin number 3)

The last parameter (9) is the number of wafer in the batch.

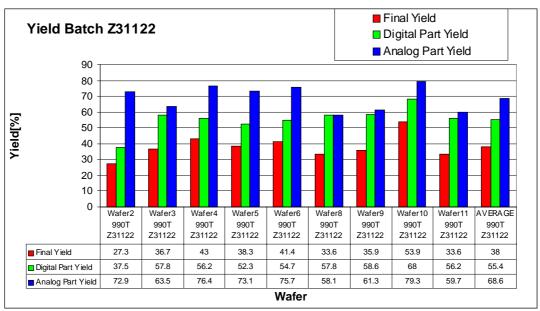

The summary bin file shows a distribution of the defects in different blocks of the chip and gives to the particular batch a kind of signature which may be used for comparison between different production lots. The summary bin file is also a basis for yield analysis. Making a simple calculation we can easily define the yield in different parts of the chip (yield in analogue part of the chip, yield in digital part of the chip and final yield for the whole die). Summing all the bins one can get the total number of dies (SUM). The number of good dies (GOOD) is the number of dies with the bin 0. Summing the dies with the bins from 2 to 8 and bins 11,12,13,14 and 16 we will get the number of dies with defects in the digital part of the chip (DIG\_DEFECTS). Summing the chips tagging with the bins number 15, 17, 20, 19, 10, 9, 18, 21 and 22 we will get the number of chips with defects in the analogue part of the chip (AN\_DEFECTS).

Then the yield can be defined as:

- Final yield [%] = 100 \* GOOD / SUM

- Digital yield [%] = 100 \* (SUM DIG\_DEFECTS) / SUM

- Analogue yield [%] = 100 \* (SUM DIG\_DEFECTS AN\_DEFECTS) / (SUM DIG\_DEFECTS)

The yield results for the analysed batch Z31122 using described formulas is shown in figure 12.

Figure 12: Yield results from batch Z31122 manufactured in March 2000.

#### 10.3. Parameters transferred to the ACCESS user database

The user database allows for distribution of the chips with a requested quality to the clients. Selection and distribution of the chips will be done based only on the chip parameters written in the database. Thus it is necessary to provide a complete list of the parameters describing the performance of the chips and their properties. The list of parameters extracted from all tests and describing the status of the chip (used, not used, destination place), batch, wafer, wafer coordinates etc. is shown in table 2. The Microsoft Access database has been used successfully during the preproduction of the ABCD chips (ABCD2NT, ABCD2T and ABCD3T coming from following lots: Z29476, Z30423, Z31122, Z34685).

| WfID       | wafer ID (wafer number)                                                         |

|------------|---------------------------------------------------------------------------------|

| Wftype     | wafer type (ABCD2T or ABCD2NT chips)                                            |

| batch      | batch number (for example Z31122)                                               |

| х,у        | chip position on the wafer                                                      |

| digflg     | digital flag - for digitally perfect chips equal to 1                           |

| Vdd0       | minimum Vdd [V] for which chip is fully efficient for all digital tests @ 50MHz |

| VddCnf0    | minimum Vdd [V] for digital TEST#1 @ 50MHz                                      |

| VddAddr0   | minimum Vdd [V] for digital TEST#2 (ADDRESSING) @ 50MHz                         |

| VddL1C0    | minimum Vdd [V] for digital TEST#2 (L1 counter) @ 50MHz                         |

| VddInpReg0 | minimum Vdd [V] for digital TEST#3 @ 50MHz                                      |

| VddInpLin0 | minimum Vdd [V] for digital TEST#4 (MASK) @ 50MHz                               |

| VddFakeS0  | minimum Vdd [V] for digital TEST#5 @50MHz                                       |

| VddSlave0  | minimum Vdd [V] for digital TEST#6 @50MHz                                       |

| VddToken0  | Minimum Vdd[V] for digital TEST#4 (TOKEN) @ 50MHz                               |

| Vdd1       | minimum Vdd[V] for which chip is fully efficient for all digital tests @ 40MHz  |

| VddCnf1    | same test as VddCnf0 @ 40MHz                                                    |

| VddAddr1   | same test as VddAddr0 @ 40MHz                                                   |

| VddL1C1    | same test as VddL1C0 @ 40MHz                                                    |

| VddInpReg1 | same test as VddInpReg0 @ 40MHz                                                 |

| VddInpLin1 | same test as VddInpLin0 @ 40MHz                                                 |

| VddFakeS1  | same test as VddFakeS0 @ 40MHz                                                  |

| VddSlave1  | same test as VddSlave0 @ 40MHz                                                  |

| VddToken1  | same test as VddToken0 @ 40MHz                                                  |

| ThrsDAC    | maximum non-linearity error for Threshold DAC ([MAX.ERROR/RANGE])               |

| -                                                                               |

|---------------------------------------------------------------------------------|

| maximum non-linearity error for Preamplifier bias DAC ([MAX.ERROR/RANGE])       |

| maximum non-linearity error for Shaper bias DAC ([MAX.ERROR/RANGE])             |

| power consumption (current) of the digital part in MASTER mode [A]              |

| power consumption (current) of the digital part in SLAVE mode [A]               |

| power consumption (current) of the analogue part in MASTER mode [A]             |

| power consumption (current) of the analogue part in SLAVE mode [A]              |

| number of dead channels (channels with defects in analogue part)                |

| number of channels with non monotonic TRIM DAC characteristic                   |

| average gain of the chip [mV/fC]                                                |

| sigma deviation of the channel gains on the chip [mV/fC]                        |

| average offset of the chip [mV]                                                 |

| sigma deviation of the channel offsets on the chip [mV]                         |

| quality factor defined as: gain/SQRT(soffset <sup>2</sup> +sgain <sup>2</sup> ) |

| number of channels with low analogue efficiency (channel with low analogue      |

| efficiency is considered as a dead channel also)                                |

| destination                                                                     |

| date of last modification                                                       |

| 0 - chip available, 1 - chip used                                               |

| no comments                                                                     |

|                                                                                 |

Table 13: List of the fields in the ACCESS database.

#### 10.4. Parameters transferred to ATLAS SCT database

For proper managing of the ABCD3T chips during the production, screening and assembling of the modules an official ATLAS SCT database is used. The list of the parameters extracted from the wafer screening transferred to that database is listed in table 14,15 and 16. All fields are mandatory.

| ITEM/CHIP uni                                                 | TYPE                                                           |             |

|---------------------------------------------------------------|----------------------------------------------------------------|-------------|

| MFR_SER_NO BATCH-WAFER-XPOS-YPOS (example Z34685-W01-X05-Y05) |                                                                | VARCHAR(32) |

|                                                               | - manufacturer serial number consist of number of batch, wafer |             |

|                                                               | number and x,y position of chip on the wafer                   |             |

| <b>RECEIPT_DATE</b>                                           | Date of reception of material (wafers)                         | VARCHAR(32) |

| LOCATION                                                      | Location of the material (for example CERN)                    | VARCHAR(32) |

Table 14: List of parameters transferred to the SCT database for the ITEM/ABCD article.

Together with the status of the chip (location, serial number, manufacturer serial number etc.) described in table 14 a set of parameters describing results of the screening tests are loaded into the database. A test data structure for the ABCD3T chips after wafer screening consist of two entities. The TEST\_ABCD article is a set of parameters extracted for the whole chip like average gain, noise, results of digital tests etc. The TESTABCDCHANNELS entity related to a given ABCD3T chip describes parameters of the single channel (gain, noise etc.) for a given channel number which is a primary key for that article.

| TEST_ABCD un | TEST_ABCD unit                                                              |              |  |

|--------------|-----------------------------------------------------------------------------|--------------|--|

| MachineName  | Name of the machine used for wafer screening                                | VARCHAR(32)  |  |

| PreampBias   | Value of bias for the preamplifier stage used in the test [uA]              | NUMBER(10,4) |  |

| ShaperBias   | Value of bias for the shaper stage used in the test [uA]                    | NUMBER(10,4) |  |

| DigFlg       | Digital flag - for digitally perfect chips equal to 1                       | NUMBER(10,4) |  |

| Vdd0         | Minimum Vdd [V] for which the chip is fully efficient for all digital tests | NUMBER(10,4) |  |

|              | @ 50MHz                                                                     |              |  |

| VddCnf0      | Minimum Vdd [V] for digital TEST#1 @ 50MHz                                  | NUMBER(10,4) |  |

| VddAddr0     | Minimum Vdd [V] for digital TEST#2 (ADDRESSING) @ 50MHz                     | NUMBER(10,4) |  |

| VddL1C0      | Minimum Vdd [V] for digital TEST#2 (L1 counter) @ 50MHz                     | NUMBER(10,4) |  |

| VddInpReg0   | Minimum Vdd [V] for digital TEST#3 @ 50MHz                                  | NUMBER(10,4) |  |

| VddInpLin0   | Minimum Vdd [V] for digital TEST#4 (MASK) @ 50MHz                           | NUMBER(10,4) |  |

| VddFakeS0    | Minimum Vdd [V] for digital TEST#5 @50MHz                                   | NUMBER(10,4) |  |

| VddSlave0    | Minimum Vdd [V] for digital TEST#6 @50MHz                                   | NUMBER(10,4) |  |

| VddToken0    | Minimum Vdd[V] for digital TEST#4 (TOKEN) @ 50MHz                           | NUMBER(10,4) |  |

| Vdd1                | Minimum Vdd[V] for which the chip is fully efficient for all digital tests                                                                                                                                                   | NUMBER(10,4)    |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| VddCnf1             | @ 40MHz<br>Same test as VddCnf0 @ 40MHz                                                                                                                                                                                      | NUMBER(10,4)    |

| VddChil<br>VddAddr1 | Same test as VddAddr0 @ 40MHz                                                                                                                                                                                                | NUMBER(10,4)    |

| VddAdd11<br>VddL1C1 | Same test as Vdd/Add/0 @ 40MHz                                                                                                                                                                                               | NUMBER(10,4)    |

| VddInpReg1          | Same test as VddInpReg0 @ 40MHz                                                                                                                                                                                              | NUMBER(10,4)    |

| VddInpLin1          | Same test as VddInpLin0 @ 40MHz                                                                                                                                                                                              | NUMBER(10,4)    |

| VddFakeS1           | Same test as VddFakeS0 @ 40MHz                                                                                                                                                                                               | NUMBER(10,4)    |

| VddSlave1           | Same test as VddSlave0 @ 40MHz                                                                                                                                                                                               | NUMBER(10,4)    |

| VddToken1           | Same test as VddToken0 @ 40MHz                                                                                                                                                                                               | NUMBER(10,4)    |

| ThrsDACSlope        | Threshold DAC slope [mV/bit] obtained from linear fit to the                                                                                                                                                                 | NUMBER(10,4)    |