SCIPP 98/05 March 3, 1998

# Irradiation Test of a GLAST Prototype Detector and a Front-end Electronics GTFE16 Chip

M. Hirayama Research Center for the Early Universe University of Tokyo

and

W. Kröger, S. Jaggar, W. Rowe, R. Johnson, and H.F.-W Sadrozinski Santa Cruz Institute for Particle Physics University of California, Santa Cruz

# 1 Introduction

The GLAST satellite will carry a pair-conversion type gamma-ray detector. A converter/tracker will consist of silicon microstrip detectors with front-end readout electronics, both of which will be exposed to radiation in orbit. An upper limit of the irradiation dose is estimated to be 10 krad over the life of GLAST. Irradiation of a silicon detector increases leakage current of the detector, which raises readout noise. Also, irradiation may do damage to the readout electronics which causes malfunctions of the electronics. To investigate the effect of irradiation of a GLAST detector and readout electronics, a prototype GLAST silicon microstrip detector was irradiated by about 10 krad at the UC Santa Cruz <sup>60</sup>Co facility. Also, a prototype GLAST front-end electronics GTFE16 chip was irradiated with the detector, and the readout noise was studied.

# 2 GLAST prototype detector

A GLAST prototype detector is an AC-coupled strip detector manufactured by Hamamatsu Photonics. The detector is  $500\mu$ m thick n-bulk with p-type strips with strip pitch of  $236\mu$ m. An implant is  $57\mu$ m wide and  $5.8 \ cm$  long, which corresponds to 7.0 pF total strip capacitance, and is biased via punch-through structures. On each strip two pads are available for the implant and the metal layer.

#### 2.1 I-V curve before irradiation

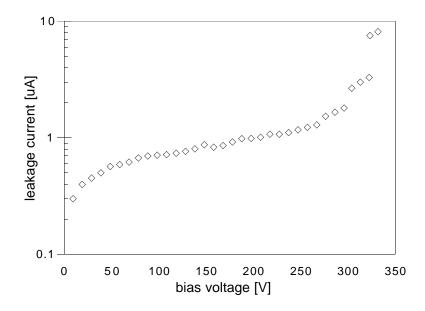

Prior to the irradiation, an I-V curve of the detector was measured (Fig. 1). All the measurements in this report were performed with bias voltage at 150 V, 200 V by a high voltage source Keithley 237, and 90–100 V by batteries (to avoid noise contamination from a high voltage source). From Fig. 1, one can see that the detector was fully depleted in the entire voltage range in which we operated it.

#### 2.2 Transient characteristics of leakage current after irradiation

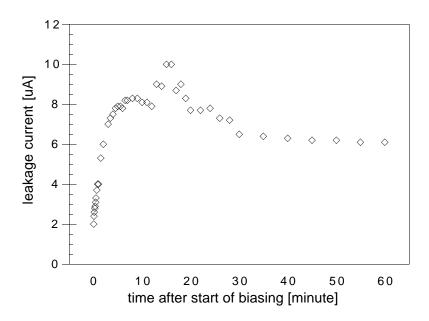

After irradiation we noticed a transient behavior of the leakage current, with a time scale of an hour. When bias voltage is applied to the detector, leakage current rapidly goes up, reaches a maximum, and decreases slowly until it is settled down. This general tendency of settling can be seen any time after the 10 krad irradiation, but maximum current seems to depend on how many days it has passed after the irradiation.

Fig. 2 shows leakage currents versus elapsed time after start of biasing measured on "day051". Because of this phenomenon we could over- or underestimate leakage currents of the detector since we are interested in leakage current during noise measurements. To avoid possible confusion due to this, we waited for about one hour before starting measurements of leakage current and readout noises after we found this phenomenon on "day006".

Fig. 1. I-V curve of the GLAST prototype detector used for an irradiation test presented in this report. The I-V curve was measured before the irradiation.

# 3 Front-end readout chip GTFE16

A front-end readout electronics "GTFE16" chip (Glast Tracker Front-end Electronics 16 channel version) was designed as a prototype of the GLAST front-end electronics. A chip has 16 channels of readout, and each channel consists of charge sensitive preamplifier and a shaping amplifier, which acts as a CR-RC filter, followed by a comparator to discriminate signals. One readout chip was used throughout all the measurements in this report. The chip was first mounted on a printed circuit board (hereafter PC board) to measure noise and gain numbers of the amplifiers.

#### 3.1 Charge injection scan

A readout chip has 4 calibration inputs, through each of which charges can be injected to 4 readout channels at the same time. A step voltage onto one of the calibration lines injects charges through a coupling capacitor of 75 fF, so the amount of charges injected can be calculated as the pulse height of the step voltage multiplied by the capacitance.

To measure readout noise and amplifier gain, we scanned the amount of charge injected through the calibration inputs with a threshold voltage fixed and counted the number of triggers. By fitting the number of triggers against the amount of charge injected with an error function, we can obtain the R.M.S. noise of a readout electronics as the width of the error function, and an amplification factor of the shaper as the median of the function. In this manner, we took three or more data points as threshold values, and fit the medians against threshold values with a straight line to estimate the amplifier gain and comparator offset. Threshold voltages were chosen so that the median appears around 1 fC, 2 fC, and 3 fC

Fig. 2. Leakage current versus elapsed time after application of detector bias, measured on 51st day after irradiation.

charge inputs for all measurements, and a couple of additional points for some (Table 1). However, only 1 fC and 2 fC data were used to estimate gain numbers, in order to avoid possible problems in a comparator function at higher threshold settings (see § B for details).

Noise and gain measurements were performed in this way as summarized in Table 1. Also, leakage currents were measured for a few strips and for a whole detector. The detector bias used when the leakage current was measured is listed in the table. In the table, a name for each noise measurement is also listed.

# 4 Noise reduction by increase of bias current into input transistor

On the PC board, there was placed a resistor connected to the VI1 input of the chip (See "GTFE16 User Guide" for details) to set the bias currents of the input transistor. Since a VI1 input always sits around 1.06 V, the bias current can be controlled by choosing a value of the resistor connected to a VI1 input. Since the noise due to the input transistor is roughly proportional to the bias current to the 1/4 power, one can reduce the intrinsic noise due to an input transistor by increasing the bias current. Since we need to see dependence of the readout noise on leakage current of a detector, we reduced the noise from the transistor by increasing the bias current.

First, noise and gain numbers were measured without any capacitive load for all 16 channels. Hereafter this first measurement is referred by "162k", because the resistor controlling the bias current was 162 k $\Omega$ . Second, the 162 k $\Omega$  resistor was replaced with a 20 k $\Omega$  resistor to increase the bias current up to ~ 200 $\mu$ A (hereafter

| Date     | Name    | Noise measured around                                        | $V_{\text{bias}}$ when $I_{\text{leak}}$ measured |

|----------|---------|--------------------------------------------------------------|---------------------------------------------------|

| 97/06/04 | 162k    | $1 \mathrm{fC},  2 \mathrm{fC}, \mathrm{and}  3 \mathrm{fC}$ | 150 V and 200 V $$                                |

| 97/06/09 | 20k     | 1  fC, 2  fC,  and  3  fC                                    | 150 V and 200 V $$                                |

| 97/06/12 | bond    | 1  fC, 2  fC,  and  3  fC                                    | 150 V and 200 V $$                                |

| 97/11/17 | bond3   | 0.5 fC, 1 fC, 2 fC, 3 fC,                                    | 150 V and 200 V $$                                |

|          |         | and 4 fC                                                     | 150 V and 200 V $$                                |

| 07/11/20 | 101 1   | • 1• •• • • • • • • • •                                      | 1.1.1.                                            |

| 97/11/20 | 10 krad | irradiation for the detector                                 | and the chip                                      |

| 97/11/20 | apres   | 1  fC, 2  fC, 3  fC,  and  4  fC                             | 150 V and 200 V                                   |

| , ,      | 1       | / / /                                                        |                                                   |

| 97/11/26 | day 006 | 1  fC, 2  fC, 3  fC,  and  4  fC                             | 150  V  and  200  V                               |

| 97/12/02 | day012  | 1  fC, 2  fC, 3  fC,  and  4  fC                             | 150  V  and  200  V                               |

| 97/12/09 | day019  | 1  fC, 2  fC, 3  fC,  and  4  fC                             | $\sim 90$ V, 150 V, and 200 V                     |

| 97/12/23 | day033  | 1  fC, 2  fC, 3  fC,  and  4  fC                             | $\sim 90$ V, 150 V, and 200 V                     |

| 98/01/10 | day051  | $1~{\rm fC},2~{\rm fC},3~{\rm fC},{\rm and}~4~{\rm fC}$      | $\sim 90$ V, 150 V, and 200 V                     |

Table 1. Overview of noise measurements

"20k"), which should reduce noise by a factor of ~ 1.7. Third, a GLAST prototype detector was loaded on the PC board and bonded to the chip (hereafter "bond").

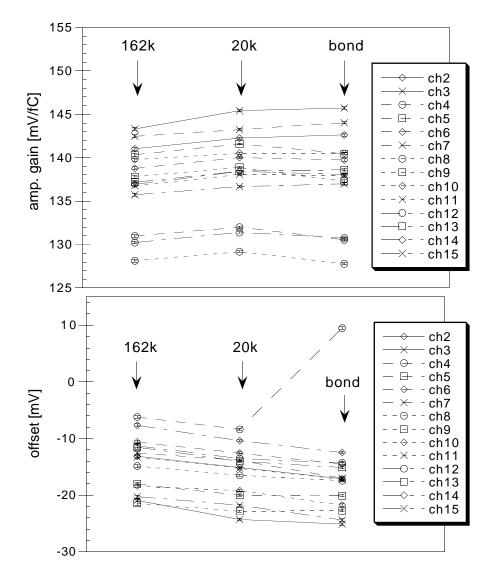

Gain numbers and comparator offsets obtained in these measurements are plotted in Fig.3 for all 16 channels. No significant changes are seen in the figure except for comparator offset in ch4.

Average and standard deviation of readout noises over ch2 through ch15 were obtained as follows:

| Exp. name | ENC [electron]  |

|-----------|-----------------|

| 162k      | $216.0\pm2.9$   |

| 20k       | $146.2 \pm 2.5$ |

| bond      | $314.8\pm5.6$   |

From the table above, one can see that the noise at "162k" is  $(1.48\pm0.03)$  times as large as those at "20k", which is close to what one expected from the increase in bias current into the first stage transistor, or 1.7. Also, comparing between "20k" and "bond", we can deduce the capacitive load dependence on readout noise as

$$\mathrm{ENC} = a + b\mathrm{C}(\mathrm{pF}),$$

where

$$a = 146.2 \pm 2.5$$

(electron)

$b = 22.8 \pm 0.8$ (electron/pF).

By multiplying  $1.48 \pm 0.03$ , which is the noise reduction factor obtained by increasing the bias current here, we obtain

$$a = 216.4 \pm 5.7 (\text{electron})$$

$b = 33.7 \pm 1.4 (\text{electron/pF}),$

Fig. 3. Gain numbers and comparator offsets of all 16 channels of GTFE16. See text for explanation for terms "162k", "20k", and "bond".

which is consistent with previous measurements by others.

For all measurements after this, the bias currents was kept at a high value (~  $200\mu$ A). The bias currents are summarized in Table 2 with names for the measurements used in this report.

Table 2. Settings of bias current into first stage transistors

| Date                 | Name             | Bias current                   | Remark                                                          |

|----------------------|------------------|--------------------------------|-----------------------------------------------------------------|

| 97/06/04             | 162k             | $21.9-22.5\mu A$               | No detector                                                     |

| 97/06/09             | 20k              | $191197\mu\text{A}$            | No detector                                                     |

| 97/06/12             | bond             | $182185\mu\text{A}$            | All channels bonded to the detector                             |

| 97/11/17             | bond3            | $194199\mu\text{A}$            | All channels except for ch0 bonded                              |

| 97/11/20<br>97/11/20 | 10 krad<br>apres | irradiation for $192-195\mu A$ | the detector and the chip<br>All channels except for ch0 bonded |

| 97/11/26             | day006           | $189-190\mu A$                 | Same as above                                                   |

| 97/12/02             | day012           | $188 - 190 \mu A$              | Same as above                                                   |

| 97/12/09             | day019           | $196 - 197 \mu A$              | Same as above                                                   |

| 97/12/23             | day 033          | $196198\mu\text{A}$            | Same as above                                                   |

| 98/01/10             | day051           | $193194\mu\text{A}$            | Same as above                                                   |

### 5 Irradiation of detector and GTFE16

The detector and the chip on a PC board were irradiated to 10 krad at the UC Santa Cruz <sup>60</sup>Co facility on Nov. 20, 1997. During the irradiation, the detector was reversely biased at ~ 90 V with batteries and the readout chip was powered in the same way as normal operation (5 V for AVDD and DVDD and 2 V for AVDD2).

#### 5.1 Radiation damage on detector

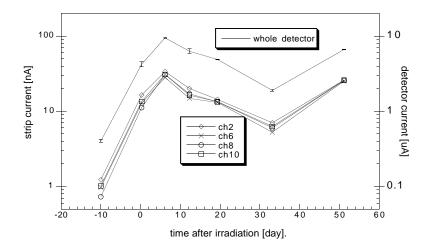

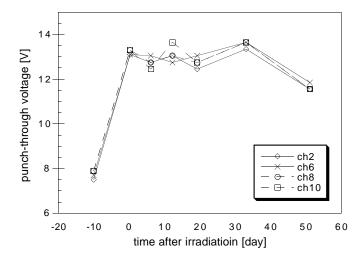

Before and after the irradiation, we systematically measured leakage currents and punch-through voltages of strips connected to ch2, 6, 8, and 10 of the readout chip. The corresponding strip numbers are 138, 134, 132, and 130, which are located almost at the center of the detector. Results are plotted in Figures 4 and 5.

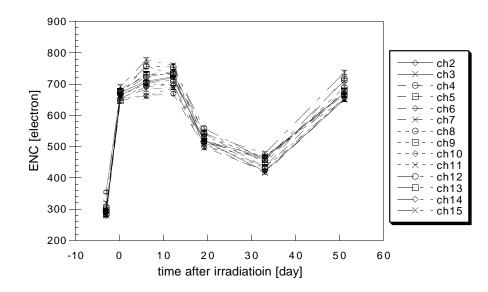

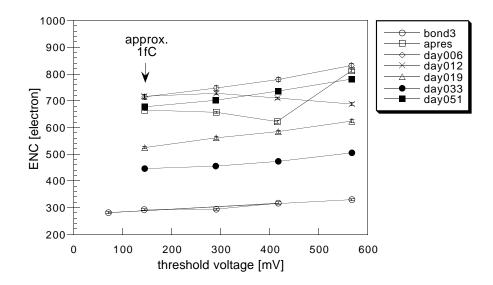

To compare with measured leakage currents, measured readout noise is plotted in Fig. 6. On the whole, measured readout noise is well correlated with measured leakage currents. Note that the readout noise was measured with a different detector bias from that used to measure the data plotted in Figures4 and 5. In the readout noise measurements  $\sim 90$ V bias was applied on the detector with batteries to avoid introducing external noise through power lines and so on.

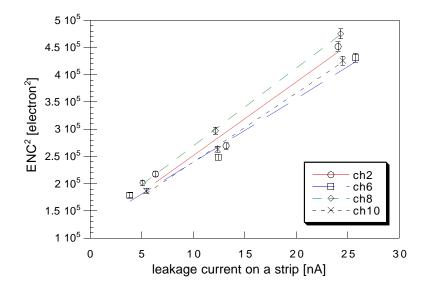

Finally, we obtained a quantitative relationship between leakage current and readout noise from measurements made on days 19, 33, and 51. We selected these three measurements, in which leakage currents on a strip were measured also for the detector biased by battery at around 90 V, which is exactly the same condition as when the readout noise was measured. Results are plotted in Fig. 7. From the figure, one can see that linear dependence of noise squared on leakage currents, as expected. The dependence is expressed as

$$\sigma^2 = \sigma_0^2 + \frac{2I_{\text{leak}}\tau F}{e} + \frac{4kT\tau F}{e^2R},$$

where  $\sigma$  is the readout noise in units of electron,  $\sigma_0$  is readout noise with pure capacitive load in the same units,  $I_{\text{leak}}$  is leakage current,  $\tau$  is shaping time which is 1.6  $\mu$ s, e is an electron charge, and F is a form factor.

By fitting  $\sigma^2$  against  $I_{\text{leak}}$ , the form factor F can be obtained as a slope. For a CR-RC filter we employ here, a form factor should be slightly less than unity if an amplifier is ideal. Since the form factors obtained range from 0.6 to 0.9, we conclude that GTFE16 works almost as expected, without any unexpected additional noise.

| Table 3. Form factors measured |                  |                |                  |  |  |

|--------------------------------|------------------|----------------|------------------|--|--|

| Charge injected                | $1  \mathrm{fC}$ | $2 \ {\rm fC}$ | $3  \mathrm{fC}$ |  |  |

| ch2                            | 0.677            | 0.824          | 0.930            |  |  |

| ch6                            | 0.587            | 0.555          | 0.646            |  |  |

| ch8                            | 0.715            | 0.802          | 0.739            |  |  |

| ch10                           | 0.633            | 0.689          | 0.821            |  |  |

Fig. 4. Leakage currents of four strips measured before and after the 10 krad irradiation. Leakage currents in the figure were measured with 150 V bias on the detector. Leakage currents measured with 200 V bias are identical. Data points at almost zero correspond to measurements made right after the irradiation.

Fig. 5. Punch-through voltages of four strips measured before and after the 10 krad irradiation. Punch-through voltages in the figure were measured with 150 V bias on the detector. Punch-through voltages measured with 200 V bias are identical. Data points at almost zero correspond to measurements made right after the irradiation.

Fig. 6. Readout noises measured for ch2 through ch15. Result on ch0 is eliminated because it is not connected to the detector and that on ch1 is not available because the channel is too noisy (see § B for details). Data points at almost zero correspond to measurements made right after the irradiation.

Fig. 7. Readout noise squared versus leakage current. In the figure is plotted noise measured on "day019", "day033", and "day051" to minimize systematic errors as discussed in § B. The readout noise plotted was measured around 1 fC injection. Plots are identical for those measured around 2 fC and 3 fC.

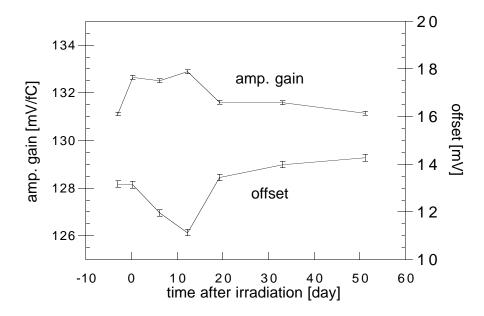

# 6 Radiation damage on the chip

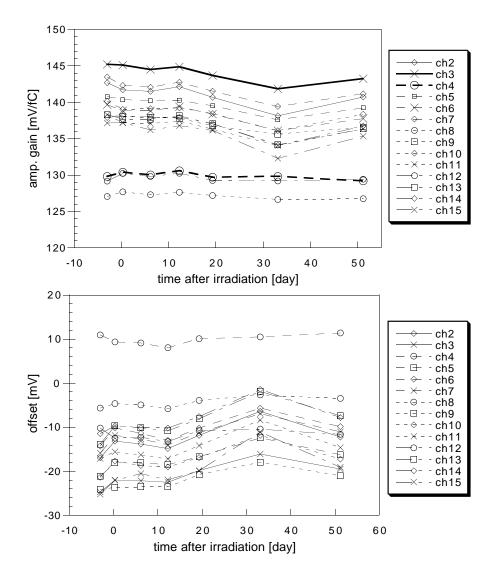

Gain numbers and comparator offsets are good measures to see radiation damage in readout electronics. The measurements are plotted in Fig. 8 for ch0, which is not connected to the detector, and in Fig. 9 for ch2 through ch15. Those for ch1 are not available because of larger noise on the channel (See § B for details). In the figure no significant change either in gain numbers or comparator offsets are seen. From these figures one can find no radiation damage seen with 10 krad  $\gamma$ radiation.

Fig. 8. Gain numbers and comparator offsets of ch0 before and after 10 krad irradiation. Data points at almost zero correspond to measurements made right after the irradiation. No change by irradiation is seen.

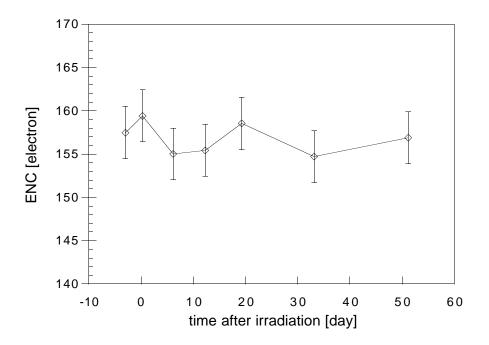

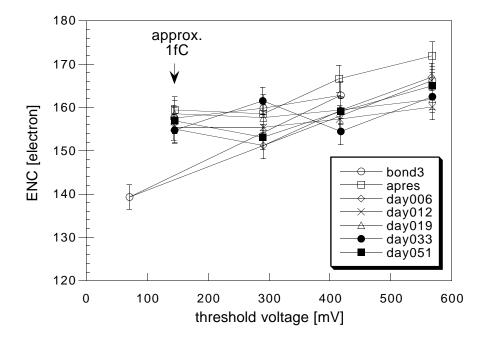

Also, the readout noise is plotted in Fig. 10 and shows no change. Again, no significant changes are seen in the figure. In conclusion, no significant damage is seen on any function of GTFE16 with 10 krad  $\gamma$ -ray radiation by the <sup>60</sup>Co source.

Fig. 9. Gain numbers (top panel) and comparator offsets (bottom) of ch2 through ch15 before and after 10 krad irradiation. The result for ch0 is eliminated because it is not connected to the detector and that on ch1 is not available because the channel is too noisy (see § B for details). Data points at almost zero correspond to measurements made right after the irradiation. No change by irradiation is seen.

Fig. 10. Comparator offsets of ch0 before and after 10 krad irradiation. Data points at almost zero correspond to measurements made right after the irradiation. No change by irradiation is seen.

## A Characteristics of GTFE16

During the irradiation test presented in this report, we investigated a few characteristics of GTFE16 such as threshold receiver response, amplifier gains, and comparator offsets.

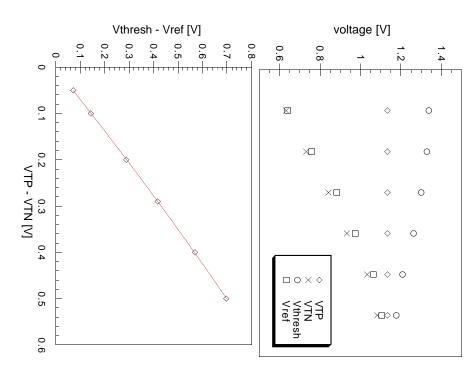

#### A.1 Threshold receiver response

Threshold receiver is designed to function as a differential amplifier, which receives voltages at VTP and VTN and outputs  $V_{\text{thresh}}$  and  $V_{\text{ref}}$ . For several settings for VTP and VTN,  $V_{\text{thresh}}$  and  $V_{\text{ref}}$  are measured as plotted in the top panel of Fig. 11. In the bottom panel in the figure are plotted the dependence of  $V_{\text{thresh}} - V_{\text{ref}}$  on VTP-VTN. We tried a fit with a 2nd order polynomial and obtained

$V_{\text{thresh}} - V_{\text{ref}} = -4.61 + 1.52x - 2.22 \times 10^{-4} x^2 (\text{mV})$

as a threshold receiver response, where x = VTP - VTN. One can see a linear term close to the design value of 1.5 and a small correction by a 2nd order term.

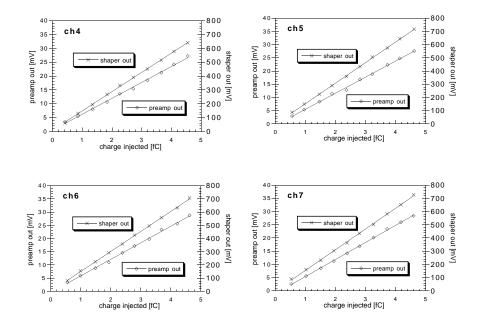

#### A.2 Direct measurement of amplifier gain and comparator offset

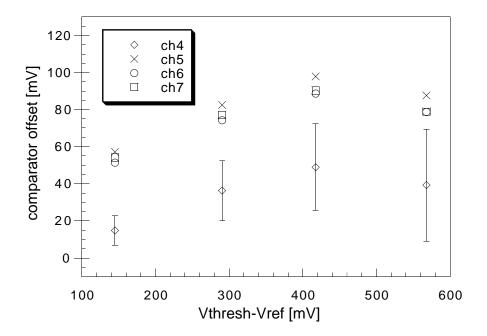

Amplifier gains and comparator offsets were measured directly by probing outputs from a preamplifier and a shaping amplifier and measuring their pulse heights. Measurements were done for ch4, 5, 6, and 7. Fig. 12 shows their pulse heights plotted against charges injected into the channel. The figure shows that both amplifiers respond linearly. From a straight line fit to these pulse heights, amplifier gains were obtained as listed in table 4.

|                              |                  | ch4  | ch5  | ch6  | ch7  | average |

|------------------------------|------------------|------|------|------|------|---------|

| chip gain                    | mV/fC            | 139  | 156  | 152  | 156  | 151     |

| $\Delta { m gain}^{\dagger}$ | %                | -7.9 | +3.3 | +6.6 | +3.3 |         |

| preamp. gain                 | $\mathrm{mV/fC}$ | 5.74 | 6.08 | 6.26 | 6.44 | 6.13    |

| $\Delta { m gain}^\dagger$   | %                | -6.4 | -0.8 | +2.1 | +5.1 |         |

| shaper gain                  | mV/mV            | 24.1 | 25.5 | 24.2 | 24.2 | 24.5    |

| $\Delta { m gain}^{\dagger}$ | %                | -1.6 | +4.1 | -1.2 | -1.2 |         |

Table 4. Direct measurement of amplifier gains

#### <sup>†</sup> Deviation from average over four channels in unit of percent

Since now we know the intrinsic amplifier gain numbers from direct measurements above, we can compute pulse heights corresponding to medians obtained from charge injection scans. Taking results from measurements "day019" as a sample, medians obtained were converted into equivalent pulse heights of shaper output and subtracted threshold voltages  $V_{\text{thresh}} - V_{\text{ref}}$ , to obtain comparator offsets for these channels. Results are plotted in Fig. 13. From the plot, one can see that approximately 0 mV for ch0 and 20 to 30 mV offsets for ch5, 6, and 7 are expected to be an extrapolation onto  $V_{\text{thresh}} - V_{\text{ref}} = 0$ , which should correspond to comparator offsets obtained by a straight line fit to medians of charge injection scans. These numbers are consistent with the results from median fitting in this report (Fig. 9).

The best-fit curve is also displayed. pendent. It can be well represented with a straight line with a small 2nd order correction. Lower panel shows  $V_{\text{thresh}} - V_{\text{ref}}$  versus VTP-VTN, which is expected to be linearly devoltage in a chip ( $V_{\text{thresh}}$  and  $V_{\text{ref}}$ ) and threshold setting from outside (VTP and VTN). Fig. 11. Threshold receiver response. Upper panel shows relationship between threshold

Fig. 12. Pulse heights of output signals from preamplifiers and from shaping amplifiers on ch4, 5, 6, and 7 for various charge injections through calibration inputs on the chip.

Fig. 13. Comparator offset directly measured in combination of charge injection scans and direct measurements of amplifier gains.

# **B** Data selection

To investigate dependence of readout noise on leakage current, we selected data measured in several ways. Here listed are data selection criteria.

- Removal of ch1 (strip #139) Readout noise on ch1 was significantly more noisy than other channels from the first. Later on it was found that the DC pad for strip #139, which is connected to ch1 of the chip, is shorted to the AC pad for strip #140, which is supposed to be connected to ch0. The short is caused by remnants of bonding on the other end of the detector than the end connected to the chip. Because of this short, noise on ch1 is not available in this report. Noise on ch0 is available except for measurement "bond" (see table 1 for terminology), since a bonding wire to the detector was removed from ch0 after that.

- Only medians measured around 1 fC and 2 fC were used for gain numbers. With the current comparator design, a comparator may function in an unexpected way when  $V_{\text{ref}}$  goes down to 0.7 V or so, which corresponds to threshold settings above 4 fC (see Fig. 11). From this, we avoided using data obtained with 4 fC injection (see table 1) for results on readout noise, gain numbers, and comparator offsets. Also, we drop the 3 fC points from a linear fit to obtain gain numbers to be safe.

- Apparent increase in readout noise with larger charge injection. With larger charge injections we also encountered a problem in measuring readout noise. Fig. 14 shows the readout noise measured with different threshold settings and averaged over ch3 through ch15. In principle, readout noise should not depend on threshold voltages. However, apparent increase in readout noises are seen in the figure. The same plot are in Fig. 15 for ch0, which is not connected to the detector. Obviously, ch0 data do not show a strong dependence of measured readout noise on threshold voltage. The apparent increase in readout noise could be due to pickup of noise originally from charge injection pulses. As the pulse goes to higher voltage, the noise pickup could increase. To avoid this possible addition to measured noise, again noise measurements with higher threshold voltages (= larger charge injection) should be eliminated from our noise study.

Fig. 14. Readout noise averaged over ch3 through ch15, measured with different threshold voltages. In principle, readout noises can be measured with any threshold voltage and such measurements should result in the same noise values. However, most of the data shows an apparent increase with threshold voltages.

Fig. 15. The same plot as Fig. 14 but for ch0, which is not connected to the detector.