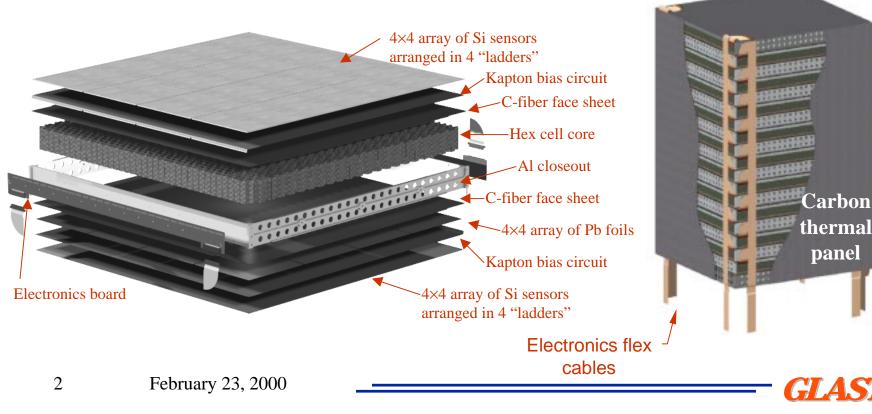

#### Overview of the Baseline Design

- 16 towers, each with 37 cm  $\times$  37 cm of Si

- 18 *x*, *y* planes per tower

- 19 "tray" structures

- 12 with 2.5%  $X_0$  Pb on bottom

- 4 with 25%  $X_0$  Pb on bottom

- 2 with no converter

- Every other tray rotated by 90°, so each Pb foil is followed immediately by an *x*, *y* plane

- 2mm gap between *x* and *y*

- Electronics on the sides of trays

- Minimize gap between towers

- 9 readout modules on each of 4 sides

- Trays stack and align at their corners

- The bottom tray has a flange to mount on the grid

- Carbon-fiber walls provide stiffness and the thermal pathway to the grid

One Tracker Tower Module

1

## Tracker Module Mechanical Design

- The tray must be very stiff to avoid collisions ( $f_0 > 500 \text{ Hz}$ ).

- All prototypes to date have been made with machined aluminum closeouts—high multiple scattering and poor thermal matching.

- A development effort is in progress at Hytec Inc. (Los Alamos, NM) to make tray structures entirely from carbon fiber.

- Hytec is also developing the carbon-fiber walls, hex-cell cores, and face sheets.

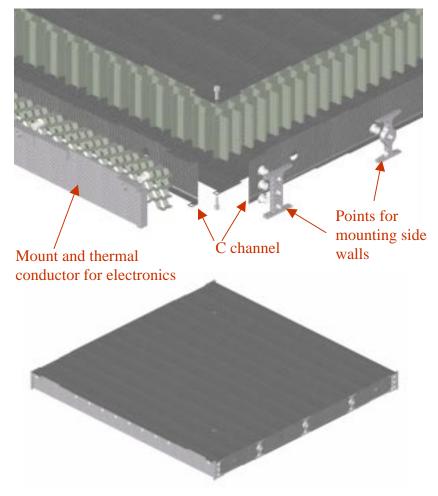

## Carbon-Composite Tray

- Honey-comb core

- we have a supplier, but price is still an issue (much higher cost than aluminum)

- Face sheets

- C-fiber already used in beam-test tower

- C-fiber is essential here for strength and for thermal matching with silicon

- Hytec has a new idea to mold in spacers on the surface for the converter foils

- Closeouts

- Simple carbon-fiber C channels on 4 sides

- Additional piece on the 2 electronics sides, machined from a 3-D resinimpregnated fiber

- Metal inserts for screws

- This is currently being prototyped, but one major remaining issue is how to treat the surface, especially in the machined areas.

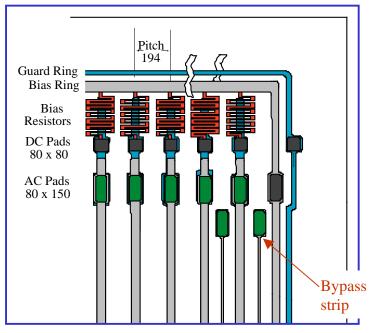

# Silicon-Strip Detectors

- 400 µm thick, single sided

- $9.2 \text{ cm} \times 9.2 \text{ cm}$  (still to be reviewed)

- Strip pitch is not finalized:

- 194  $\mu m$  pitch in beam test module

- $-~201\,\mu m$  in the NASA proposal

- May have to increase to 235 μm or 282 μm, depending on power allocation

- AC coupled with polysilicon bias (~60MΩ)

- Beamtest module: 296 detectors from 4" wafers and 251 from 6" wafers from HPK, plus 5 of the large size from Micron.

- Typical leakage: 300 nA/detector (HPK)

- Bad strips: about 1 in 5000

- 35 9.5-cm square detectors from HPK

- Prototypes on order from STM

Schematic layout of the proto detectors.

- Bypass strips will not be used.

- DC pads will increase in size.

- A second AC pad will be added on each strip, for probing and for a second chance at wire bonding.

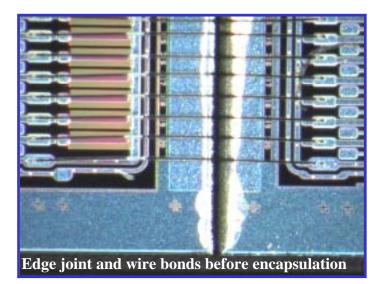

## Si Detector Ladders

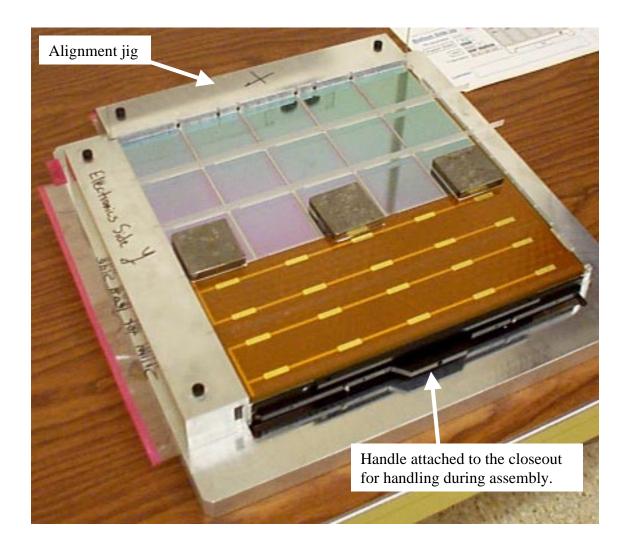

- Detectors were edge bonded at SLAC by hand, using a simple alignment jig.

- Some problems with vertical steps on the larger detectors.

- Not ideal control of the amount of epoxy in the joint (a few joints failed during later handling).

- Bond-line thickness set by hand and amount of adhesive.

- Alignment in the plane:  $\sim 30 \ \mu m \ typ$ .

- Wire bonding is straightforward.

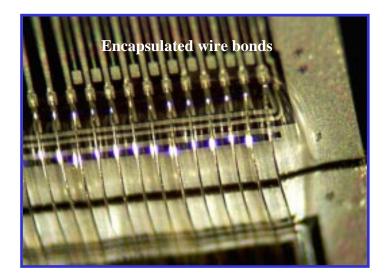

- Wire bonds were encapsulated with a hard curing epoxy.

- Epoxy was sprayed onto the bonds through a slit.

- Control was by hand and eye (tedious).

- There was some overspray.

- More efficient methods need to be investigated. Or is it even needed?

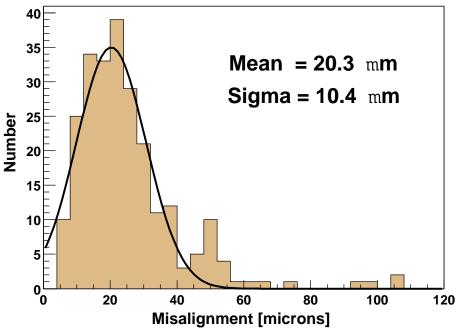

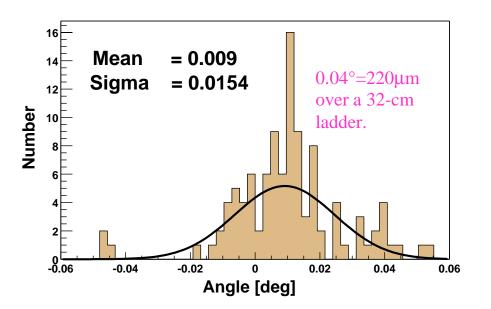

### Ladder Survey for the Beam-test Tracker

- The ladders all were surveyed on an automated optical measuring stage.

- Most of the ladders were adequate, but we are not satisfied with those with  $>50 \ \mu m$  deviations.

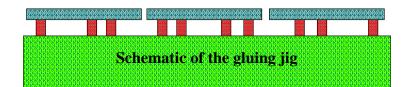

The gluing jig was built for ladders made from 5 small detectors. The larger detectors were not optimally supported, such that any deviation from flatness results in z steps.

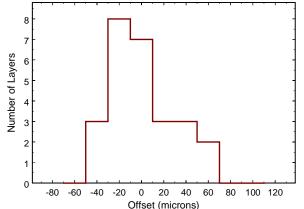

For each ladder, the maximum deviation of the fiducial marks from a straight-line fit is entered into this histogram.

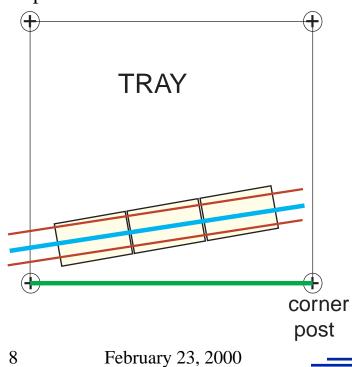

## Ladder Placement on Trays

- Ladders were aligned with respect to the holes in the corner posts, by pressing against a straight edge.

- Shims set the spacing between ladders.

- Silver-loaded epoxy was used to bond detectors to the bias circuit.

- 50 µm thick tape set the adhesive bond thickness.

- This procedure relies upon accurate dicing of the detector wafers.

- Lots of issues with adhesives still need to be worked out.

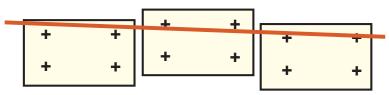

### Alignment of Ladders in Trays

- All 17 beam-test trays were optically surveyed on the automated measuring stage.

- Lines were fit to the detector fiducial marks in a ladder and the angle measured with respect to a line between the centers of the corner posts.

- The results, shown above, are not as good as desired (<0.02°), indicating improvements needed in the jigs and procedures.

- 3 ladders are off by >0.04° due to a known mistake on one tray (a shim slipped out), but it is not yet understood why others are off by similar amounts (partly due to slippage on the surveying stage).

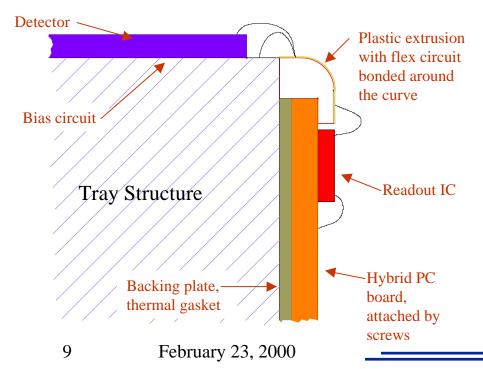

- Detector bias: 2-layer Kapton flex circuit

- Top layer: pads for conductive adhesive, to carry the bias current to the detectors.

- Bottom layer: hatched ground plane, to isolate the detector bias from the conductive tray structure.

- Standard space-qualified industrial processes are adequate for this.

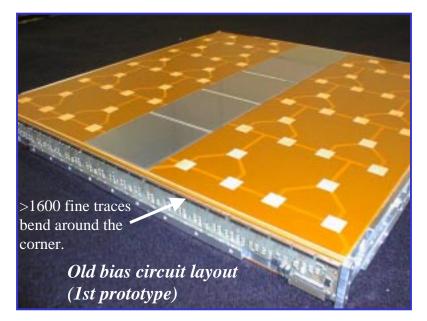

New concepts under development:

- The bias circuit HV and ground plane are divided into 4 separate circuits. We need to reevaluate the gluing pattern.

- The flex circuit for wrapping around the corner is separate from the bias circuit and is part of the hybrid assembly. It has 1 trace for each detector strip, plus bias and ground connections for each ladder.

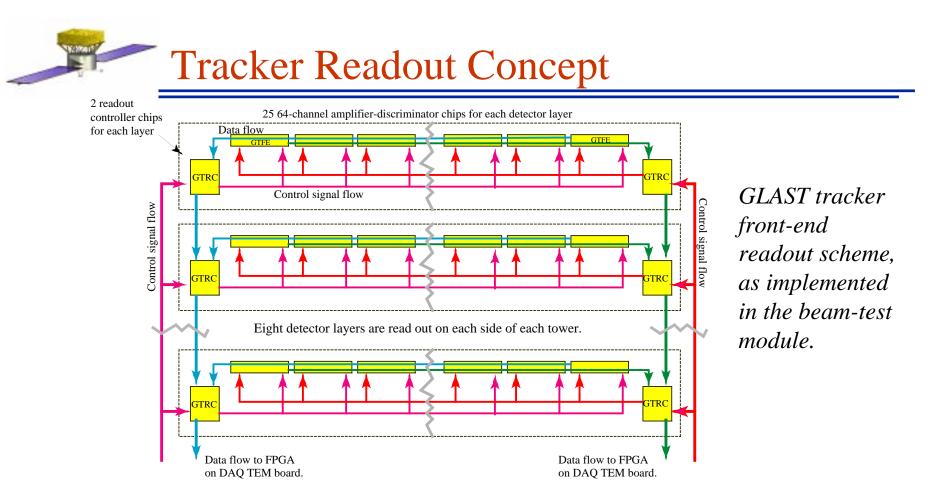

- Two redundant paths for control signals, trigger information, and data output.

- Any single chip or cable can go bad without affecting the readout of the remaining chips.

- Zero-suppressed data from the entire tower flows out in one, or two, serial data streams.

- In the front-end chips (GTFE) zeros are suppressed only if the entire 64-channel chip has no hits.

- Complete zero suppression and formatting takes place in the digital GTRC chips.

- 10 February 23, 2000

**GLAST**

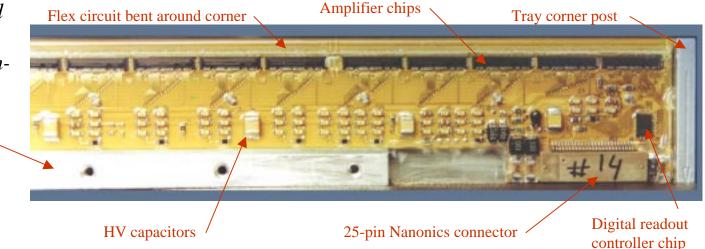

Hybrid mounted on a completed tray of the beamtest module.

Boss for mechanical and thermal attachment to the wall.

- 25 64-channel amplifier chips and 2 digital readout chips on beam-test hybrid.

- 8-layer standard FR4 PC board with minimum 100 micron traces and spaces.

- Gold body for wire bonding.

- Lots of filtering and decoupling for bias, power supplies, etc.

- Fuses on the power supplies.

- Temperature monitor.

- Careful attention to shielding between analog and digital and to maintaining clean current returns for the detector signals.

- Still needs a lot of work to bring the design & fab up to space qualification levels.

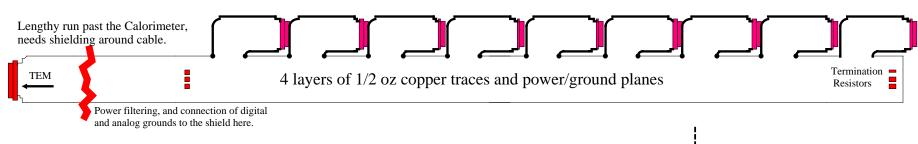

Tracker Readout Cables

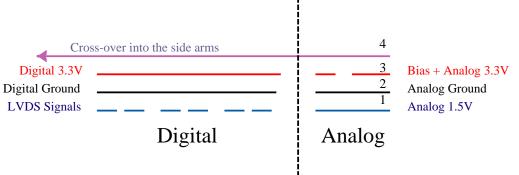

- Custom 4-layer flex circuits

- Standard processes, with Kapton and 1/2 oz copper.

- Connectors and other components are surface-mount soldered.

4-layer cable cross section, showing a schematic representation of the arrangement of conductors.

#### Outstanding issues:

- Detailed design changes with respect to what is in the beam-test version.

- Finding a manufacturer who can do the full length (or design a splice in the center).

- Shielding while going past the calorimeter.

- Space qualification.

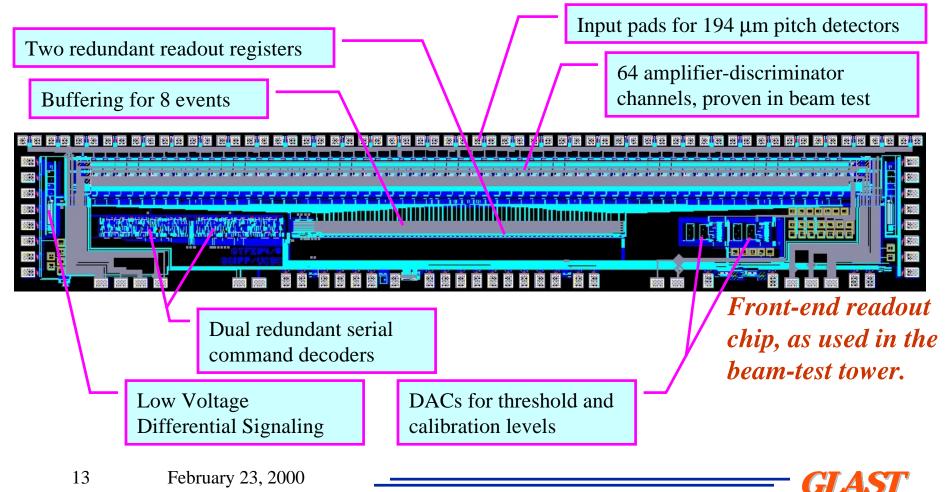

## Front-End Readout Chip (GTFE64)

- Several thousand were made in the HP 0.8  $\mu$ m process for the beam-test tower and gave very good performance. This process no longer exists.

- Prototypes of just the amplifiers and discriminators fabricated in the HP 0.5  $\mu$ m process are under test at UCSC and, preliminarily, appear to be working well.

## Readout Controller Chip (GTRC)

- Full custom CMOS IC, fabricated in the HP 0.8µm process for the beam-test tower.

- Logic design and layout uses DoD standard cells.

- Functions:

- Zero suppression and formatting of the data.

- Command and clock interface to the front-end chips.

- Sequencing and buffering of the readout.

- Time-over-threshold of the Fast-OR trigger output.

- Communication via low-voltage differential signaling (LVDS).

- Functioned reliably in the beam test.

- Next version will be done in the HP 0.5 μm process.

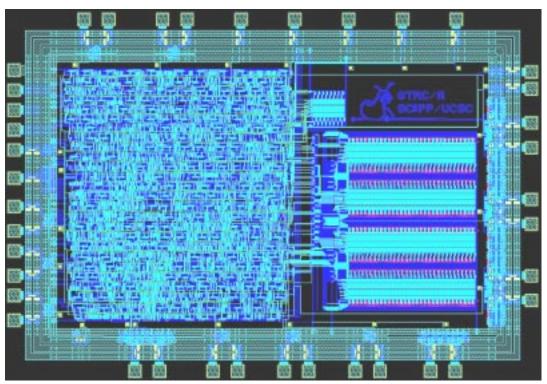

Cadence layout of the GLAST Tracker Readout Controller chip (GTRC). The left half is logic made from standard cells, while the right half is memory for buffering.

- A number of detailed design mods are being considered (pending a formal review of the tracker electronics design)

- New detector pitch

- Output information to allow buffer management to be verified

- Larger wire bonding pads

- Metalize back of chip

- Separate thresholds for data and trigger?

- etc.

- Engineering manpower: it isn't clear that we have an engineer to redo the GTRC chip design, simulation, and layout, including the new design modifications.

- Radiation hardness:

- Total dose is very unlikely to be a problem (less than 10 kRad).

- Single-event latchup: published measurements on the HP 0.5 μm process appear to exceed requirements. How to test?

- Single-event upset: we are working to implement SEU-safe flip flops for the configuration register.

- Space qualification:

- This needs to be researched. We do not yet understand all of the requirements that might be imposed.

- Time is short: final prototypes need to be ready for the engineering model by mid 2001.

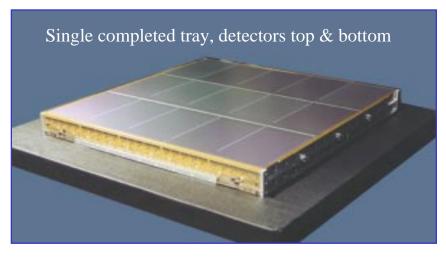

## Beam-Test Engineering Model Tracker

- 16 x, y planes

- 51,200 amplifier-discriminator channels, with 41,600 connected to detector strips.

- 130 32-cm detector ladders (out of 160 needed for the complete device), for 2.6 m<sup>2</sup> of silicon.

- VME-base DAQ card with 2 FPGAs, one for readout and one for the trigger.

- Aluminum tray closeouts and cores, with 75  $\mu$ m thick carbon-composite face sheets.

- 11 *x*, *y* planes with 3.5% Pb foils

- 3 *x*,*y* planes with 25% Pb foils

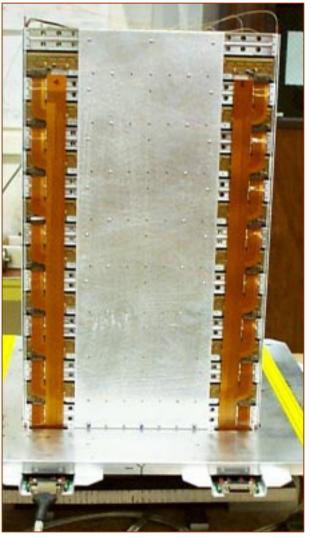

The completed beam-test tracker, with 2 side panels removed.

#### Some of the Testing Done:

- Detectors tested by manufacturer (IV and coupling cap) and visually scanned by us.

- IV curves taken again after edge bonding, wire bonding, and before mounting on the tray.

- Capacitance measured on an automatic probe station for each strip after wire bonding to detect broken caps, broken metal, missing wire bonds, and shorts. *Only 18 bad strips found and isolated by removing wire bonds.*

- ICs thoroughly tested on the wafer by an automatic probe station.

- Hybrids tested and burned in before mounting on trays.

- The result is only a handful of dead or noisy channels, plus one noisy ladder (unknown reason).

Setup used to test 8 trays at a time with cosmic-rays and the actual DAQ. The trays are still in protective plastic enclosures and have aluminum handles attached to the sides.

## **Beam-Test Tracker Performance**

No real analysis of the PSF for photon conversions is done yet, but good progress has been made on putting together the reconstruction software.

Data were taken for

- cosmic rays

- positrons at various energies

- tagged photons

- mixture of hadrons and positrons

The tracker ran reliably for 2 months with no changed needed in threshold settings or masks (no channels were masked) and no change in leakage.

The self trigger worked well, but most data were taken with a beam trigger.

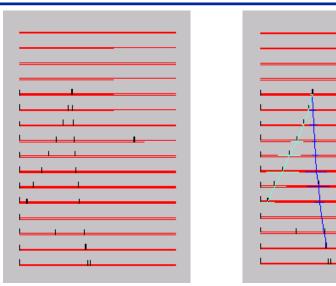

A single photon conversion from beam-test data, before and after track finding and fitting with a Kalman-Filter algorithm.

Distribution of photon-conversions per tracker plane.

Tracker Tower Alignment

- Tray-to-tray alignment has been looked at in cosmic-ray and positron data and appears to be within our goal of 50 micron rms.

- More analysis is in progress with a position scan of hadron data, to get uniform coverage and enough sensitivity to study rotations.

Offsets from 26 of the 32 layers, as obtained from 20-GeV positrons.

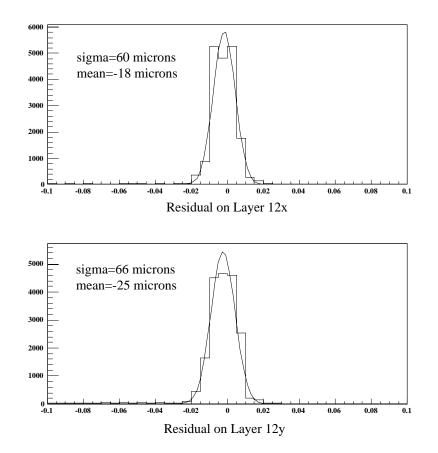

Residual distributions on Layer 12, from fitting 20-GeV positron tracks to straight lines in layers above and below. The width is as expected for 194 µm pitch.

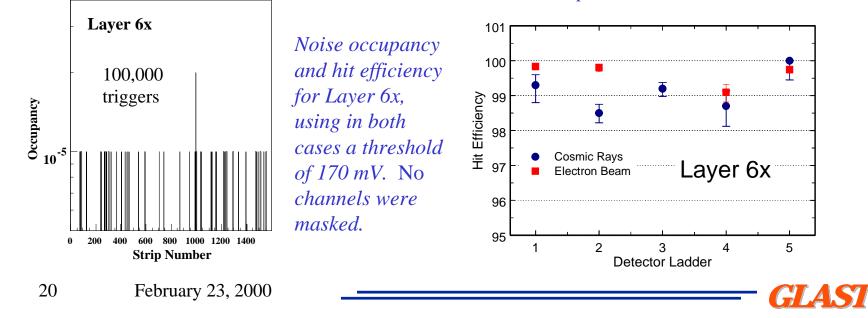

### **Tracker Noise and Efficiency**

1.1

1.0

0.9

0.8

- Noise occupancy was obtained by inducing triggers, followed by readout, at random times.

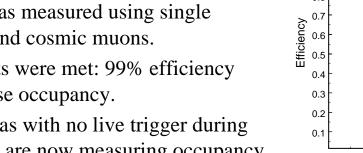

- Hit efficiency was measured using single electron tracks and cosmic muons.

- The requirements were met: 99% efficiency with  $<<10^{-4}$  noise occupancy.

- However, this was with no live trigger during the readout. We are now measuring occupancy during digital activity.

0 200 400 600 800 1000 1200 1400 Threshold (mV) Hit efficiency versus threshold for 5 GeV positrons.

Layer 10 x

Layer 10 v

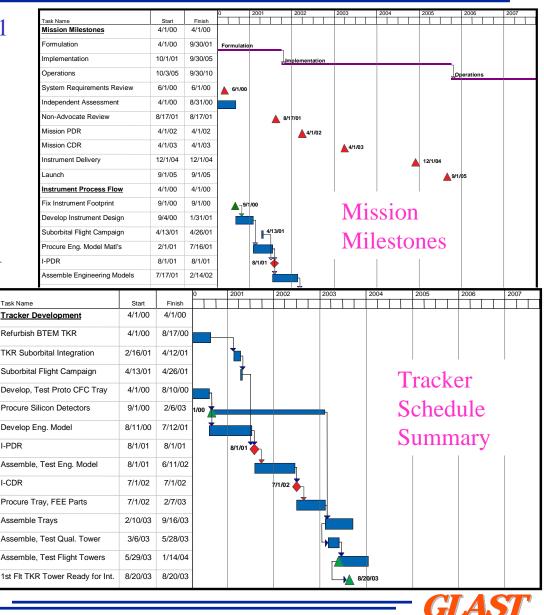

#### Formulation Phase: through 9/30/01

- Design must be finalized

- Culminates in Instrument PDR

- Si procurement begins 9/1/00! Start building ladders asap

- Balloon test, April 01?

#### **Implementation Phase:**

- Build engineering model before CDR

- Instrument CDR on 7/1/02

- Start tray assembly on 2/10/03

- 1st tower done by 8/20/03

- Final tower done by 1/14/04

Summary of Work in Progress

- Settle on final parameters: size, pitch, number of layers, Pb converter distribution.

- Budgets, schedules, and system engineering.

- Construction of fabrication facilities at SLAC.

- Carbon-composite tray structure design and prototyping.

- Review tracker electronics and then redo all of the designs:

- Front-end readout chip

- Readout controller chip

- Hybrid, including the new scheme to bend around the corner

- Bias circuit

- Kapton cables

- Prefabrication runs of the detectors.

- Long term testing of detectors, including effects of adhesives.

- Thermal testing of detector ladders on face sheets + Pb (strain and IV).

- Further development of tray assembly procedures

- Ladder construction & encapsulation

- Ladder placement

- Hybrid attachment and encapsulation

- QC & documentation (ISO9000)

- Analysis of beam-test data.

- Further testing of the beam-test tracker electronics.

- Reconstruction and Monte-Carlo software development.

- Balloon test preparations.